基于AT32UC3A EVK1105設(shè)計(jì)的32位MCU開發(fā)技術(shù)

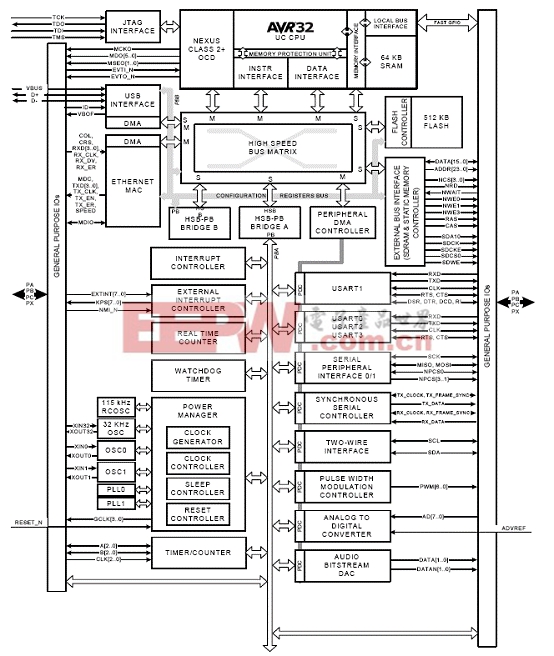

AT32UC3A是完整的系統(tǒng)級芯片微控制器,采用VR32 UC RISC,工作頻率高達(dá)66MHz,設(shè)計(jì)用于對成本敏感的嵌入式應(yīng)用,特別是低功耗,高代碼效率和高性能. AT32UC3A還集成了閃存和SRAM存儲器,外設(shè)直接存儲器訪問控制器(PDCA),以及PowerManager電源管理.此外還有多種通信接口如UART,SPI,TWI,同步串行控制器,USB和以太網(wǎng)MAC等.本文介紹了AT32UC3A主要特性, 方框圖以及32位AVR EVK1105評估板特性,詳細(xì)電路圖和材料清單(BOM).

AVR®32 32-Bit Microcontroller

The AT32UC3A is a complete System-On-Chip microcontroller based on the AVR32 UC RISC processor running at frequencies up to 66 MHz. AVR32 UC is a high-performance 32-bit RISC microprocessor core, designed for cost-sensitive embedded applications, with particular emphasis on low power consumption, high code density and high performance.

The processor implements a Memory Protection Unit (MPU) and a fast and flexible interrupt controller for supporting modern operating systems and real-time operating systems. Higher computation capabilities are achievable using a rich set of DSP instructions.

The AT32UC3A incorporates on-chip Flash and SRAM memories for secure and fast access. For applications requiring additional memory, an external memory interface is provided on AT32UC3A0 derivatives.

The Peripheral Direct Memory Access controller (PDCA) enables data transfers between peripherals and memories without processor involvement. PDCA drastically reduces processing overhead when transferring continuous and large data streams between modules within the MCU.

The PowerManager improves design flexibility and security: the on-chip Brown-Out Detector monitors the power supply, the CPU runs from the on-chip RC oscillator or from one of external oscillator sources, a Real-Time Clock and its associated timer keeps track of the time.

The Timer/Counter includes three identical 16-bit timer/counter channels. Each channel can be independently programmed to perform frequency measurement, event counting, interval measurement, pulse generation, delay timing and pulse width modulation.

The PWM modules provides seven independent channels with many configuration options including polarity, edge alignment and waveform non overlap control. One PWM channel can trigger ADC conversions for more accurate close loop control implementations.

The AT32UC3A also features many communication interfaces for communication intensive applications. In addition to standard serial interfaces like UART, SPI or TWI, other interfaces like flexible Synchronous Serial Controller, USB and Ethernet MAC are available.

The Synchronous Serial Controller provides easy access to serial communication protocols and audio standards like I2S.

The Full-Speed USB 2.0 Device interface supports several USB Classes at the same time

thanks to the rich End-Point configuration. The On-The-GO (OTG) Host interface allows device like a USB Flash disk or a USB printer to be directly connected to the processor.

The media-independent interface (MII) and reduced MII (RMII) 10/100 Ethernet MAC module provides on-chip solutions for network-connected devices.

AT32UC3A integrates a class 2+ Nexus 2.0 On-Chip Debug (OCD) System, with non-intrusive real-time trace, full-speed read/write memory access in addition to basic runtime control.

AT32UC3A主要特性:

High Performance, Low Power AVR®32 UC 32-Bit Microcontroller

C Compact Single-cycle RISC Instruction Set Including DSP Instruction Set

C Read-Modify-Write Instructions and Atomic Bit Manipulation

C Performing 1.49 DMIPS / MHz

Up to 91 DMIPS Running at 66 MHz from Flash (1 Wait-State)

Up to 49 DMIPS Running at 33MHz from Flash (0 Wait-State)

C Memory Protection Unit

Multi-hierarchy Bus System

C High-Performance Data Transfers on Separate Buses for Increased Performance

C 15 Peripheral DMA Channels Improves Speed for Peripheral Communication

Internal High-Speed Flash

C 512K Bytes, 256K Bytes, 128K Bytes Versions

C Single Cycle Access up to 33 MHz

C Prefetch Buffer Optimizing Instruction Execution at Maximum Speed

C 4ms Page Programming Time and 8ms Full-Chip Erase Time

C 100,000 Write Cycles, 15-year Data Retention Capability

C Flash Security Locks and User Defined Configuration Area

Internal High-Speed SRAM, Single-Cycle Access at Full Speed

C 64K Bytes (512KB and 256KB Flash), 32K Bytes (128KB Flash)

External Memory Interface on AT32UC3A0 Derivatives

C SDRAM / SRAM Compatible Memory Bus (16-bit Data and 24-bit Address Buses)

Interrupt Controller

C Autovectored Low Latency Interrupt Service with Programmable Priority

System Functions

C Power and Clock Manager Including Internal RC Clock and One 32KHz Oscillator

C Two Multipurpose Oscillators and Two Phase-Lock-Loop (PLL) allowing Independant CPU Frequency from USB Frequency

C Watchdog Timer, Real-Time Clock Timer

Universal Serial Bus (USB)

C Device 2.0 Full Speed and On-The-Go (OTG) Low Speed and Full Speed

C Flexible End-Point Configuration and Management with Dedicated DMA Channels

C On-chip Transceivers Including Pull-Ups

Ethernet MAC 10/100 Mbps interface

C 802.3 Ethernet Media Access Controller

C Supports Media Independent Interface (MII) and Reduced MII (RMII)

One Three-Channel 16-bit Timer/Counter (TC)

C Three External Clock Inputs, PWM, Capture and Various Counting Capabilities

One 7-Channel 16-bit Pulse Width Modulation Controller (PWM)

Four Universal Synchronous/Asynchronous Receiver/Transmitters (USART)

C Independant Baudrate Generator, Support for SPI, IrDA and ISO7816 interfaces

C Support for Hardware Handshaking, RS485 Interfaces and Modem Line

Two Master/Slave Serial Peripheral Interfaces (SPI) with Chip Select Signals

One Synchronous Serial Protocol Controller Supports I2S and Generic Frame-Based Protocols

One Master/Slave Two-Wire Interface (TWI), 400kbit/s I2C-compatible

One 8-channel 10-bit Analog-To-Digital Converter

16-bit Stereo Audio Bitstream

C Sample Rate Up to 50 KHz

On-Chip Debug System (JTAG interface)

C Nexus Class 2+, Runtime Control, Non-Intrusive Data and Program Trace

100-pin TQFP (69 GPIO pins), 144-pin LQFP (109 GPIO pins) , 144 BGA (109 GPIO pins)

5V Input Tolerant I/Os

Single 3.3V Power Supply or Dual 1.8V-3.3V Power Supply

圖1.AT32UC3A方框圖

32位AVR EVK1105評估板

The 32-bit AVR EVK1105 is an evaluation kit for the AT32UC3A0512 which demonstrates Atmels state-of-the-art 32-bit AVR microcontroller in Hi-Fi audio decoding and streaming applications. The kit contains reference hardware and software for generic MP3 player docking stations.

圖2.32位AVR EVK1105評估板外形圖

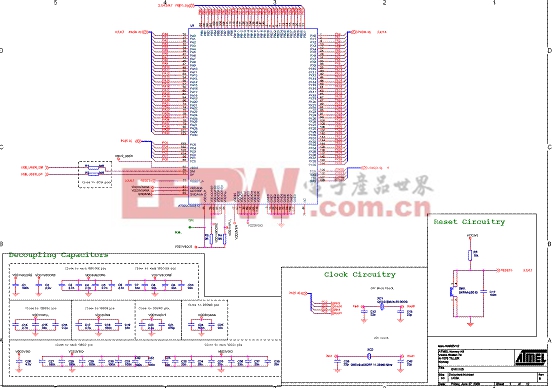

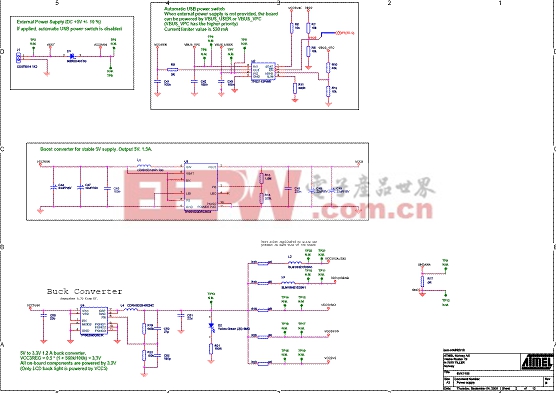

32位AVR EVK1105評估板電路圖和BOM:

圖3.32位AVR EVK1105評估板電路圖(1)

評論