Intersil ISL62882移動(dòng)CPU多相PWM穩(wěn)壓方案

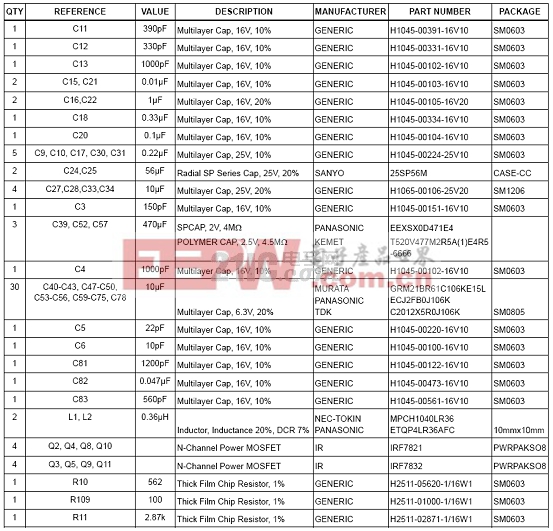

1相GPU應(yīng)用參考設(shè)計(jì)電路材料清單:

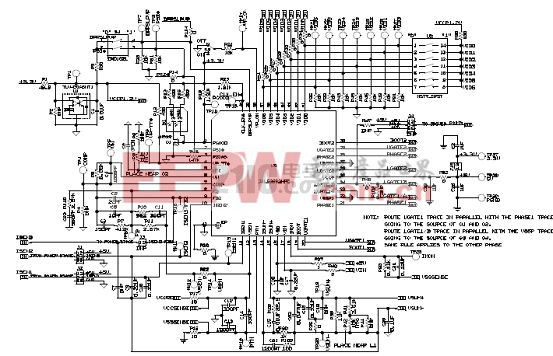

圖4.2相GPU應(yīng)用參考設(shè)計(jì)電路

2相GPU應(yīng)用參考設(shè)計(jì)電路材料清單:

ISL62882EVAL2Z評(píng)估板

The ISL62882EVAL2Z evaluation board demonstrates the performance of the ISL62882 multiphase synchronous-buck PWM VCORE controller implementing Intel IMVP-6.5 protocol. The ISL62882 features Intersils Robust Ripple Regulator (R3) technology. An on-board dynamic-load generator is included for evaluating the transient-load response. It applies a 300μs pulse of approximately 25mΩ load across VO and PGND

ISL62882EVAL2Z Schematic

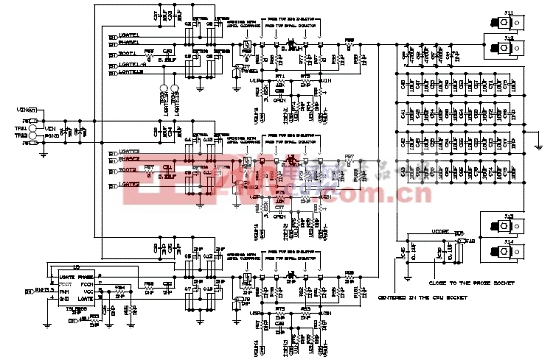

圖5.ISL62882EVAL2Z評(píng)估板電路圖(1)

圖6.ISL62882EVAL2Z評(píng)估板電路圖(2)

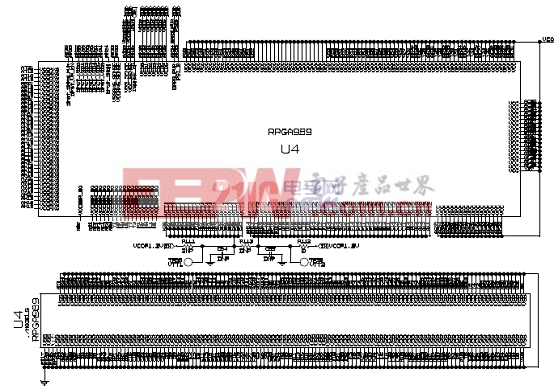

圖7.ISL62882EVAL2Z評(píng)估板電路圖(3)

評(píng)論