stm32 時(shí)鐘設(shè)置函數(shù)分析

/* SYSCLK, HCLK, PCLK2 and PCLK1 configuration ---------------------------*/

這個(gè)函數(shù)的主要目的是 設(shè)置以上4個(gè)時(shí)鐘的,那這四個(gè)時(shí)鐘主要是用來(lái)干什么的?

這個(gè)后面再分析。

先看怎么獲取72M的頻率

/* Enable HSE */ 打開(kāi)外部高速時(shí)鐘

RCC->CR |= ((uint32_t)RCC_CR_HSEON);

等待時(shí)鐘穩(wěn)定

/* Wait till HSE is ready and if Time out is reached exit */

do

{

HSEStatus = RCC->CR & RCC_CR_HSERDY;

StartUpCounter++;

} while((HSEStatus == 0) && (StartUpCounter != HSE_STARTUP_TIMEOUT));

if ((RCC->CR & RCC_CR_HSERDY) != RESET)

{

HSEStatus = (uint32_t)0x01;

}

else

{

HSEStatus = (uint32_t)0x00;

}

如果時(shí)鐘穩(wěn)定了

if (HSEStatus == (uint32_t)0x01)

{

/* Enable Prefetch Buffer */

FLASH->ACR |= FLASH_ACR_PRFTBE;

/* Flash 2 wait state */

FLASH->ACR &= (uint32_t)((uint32_t)~FLASH_ACR_LATENCY);

FLASH->ACR |= (uint32_t)FLASH_ACR_LATENCY_2;

/* HCLK = SYSCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;///*!< SYSCLK not divided */

/* PCLK2 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1;///*!< HCLK not divided */

/* PCLK1 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV2;///*!< HCLK not divided */

#ifdef STM32F10X_CL

這一段互聯(lián)型的產(chǎn)品的描述 刪掉

#else

開(kāi)始設(shè)置倍頻 9倍頻

/* PLL configuration: PLLCLK = HSE * 9 = 72 MHz */

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_PLLSRC | RCC_CFGR_PLLXTPRE |

RCC_CFGR_PLLMULL));

RCC->CFGR |= (uint32_t)(RCC_CFGR_PLLSRC_HSE | RCC_CFGR_PLLMULL9);

#endif /* STM32F10X_CL */

/* Enable PLL */ 打開(kāi)PLL

RCC->CR |= RCC_CR_PLLON;

/* Wait till PLL is ready */ 等待PLL穩(wěn)定

while((RCC->CR & RCC_CR_PLLRDY) == 0)

{

}

/* Select PLL as system clock source */ 選中PLL 作為時(shí)鐘源

也就是切換系統(tǒng)時(shí)鐘

RCC->CFGR &= (uint32_t)((uint32_t)~(RCC_CFGR_SW));

RCC->CFGR |= (uint32_t)RCC_CFGR_SW_PLL;

/* Wait till PLL is used as system clock source */ 等待系統(tǒng)時(shí)鐘源的切換

因?yàn)橄到y(tǒng)剛開(kāi)始(從復(fù)位到這一步)不是以PLL作為時(shí)鐘源的。

while ((RCC->CFGR & (uint32_t)RCC_CFGR_SWS) != (uint32_t)0x08)

{

}

到這里,在來(lái)看剛剛開(kāi)始問(wèn)題/* SYSCLK, HCLK, PCLK2 and PCLK1 configuration ---------------------------*/

這幾個(gè)時(shí)鐘 都是用來(lái)做什么的。

配置情況

/* HCLK = SYSCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_HPRE_DIV1;///*!< SYSCLK not divided */

/* PCLK2 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE2_DIV1;///*!< HCLK not divided */

/* PCLK1 = HCLK */

RCC->CFGR |= (uint32_t)RCC_CFGR_PPRE1_DIV2;///*!< HCLK not divided */

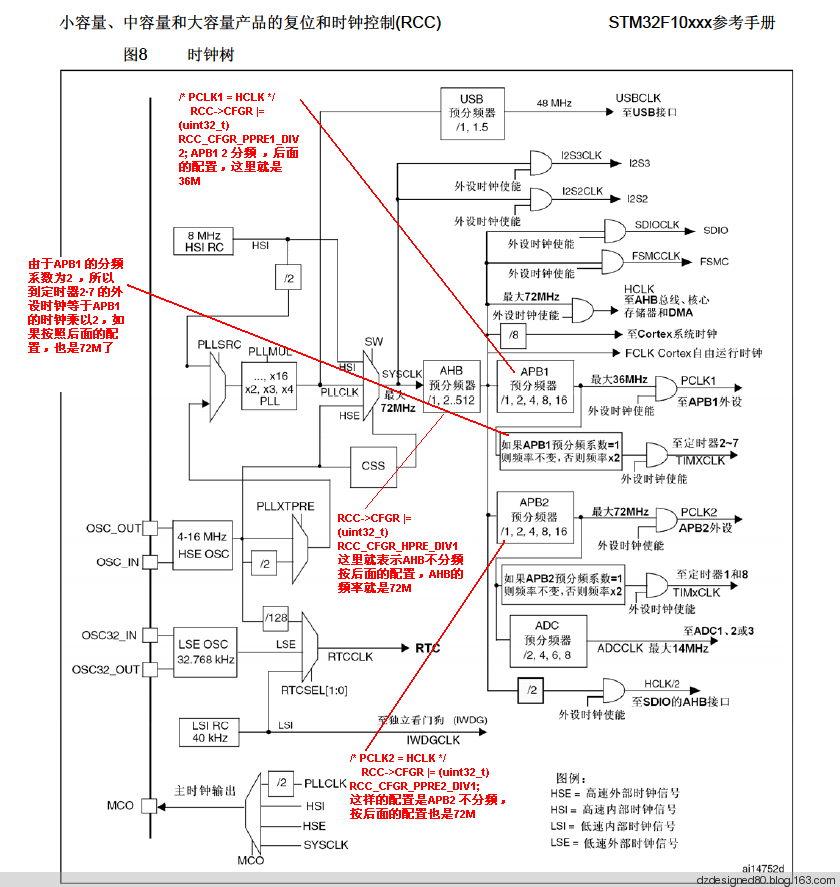

還是要看時(shí)鐘樹(shù):

時(shí)鐘樹(shù):

PCLK2 就是APB2時(shí)鐘

PCLK1 就是APB1時(shí)鐘 ,系統(tǒng)里面的注釋還有點(diǎn)錯(cuò)誤,APB1應(yīng)該=1/2 HCLk

SYSCLK就是PLL時(shí)鐘輸入

評(píng)論