stm32 SPI 接口

SPI 是英語Serial Peripheral interface的縮寫,顧名思義就是串行外圍設(shè)備接口。是Motorola首先在其MC68HCXX系列處理器上定義的。SPI接口主要應(yīng)用在 EEPROM,F(xiàn)LASH,實(shí)時(shí)時(shí)鐘,AD轉(zhuǎn)換器,還有數(shù)字信號處理器和數(shù)字信號解碼器之間。SPI,是一種高速的,全雙工,同步的通信總線,并且在芯片的管腳上只占用四根線,節(jié)約了芯片的管腳,同時(shí)為PCB的布局上節(jié)省空間,提供方便,正是出于這種簡單易用的特性,現(xiàn)在越來越多的芯片集成了這種通信協(xié)議,STM32也有SPI接口。

SPI接口一般使用4條線:

MISO 主設(shè)備數(shù)據(jù)輸入,從設(shè)備數(shù)據(jù)輸出。 MOSI 主設(shè)備數(shù)據(jù)輸出,從設(shè)備數(shù)據(jù)輸入。 SCLK時(shí)鐘信號,由主設(shè)備產(chǎn)生。 CS從設(shè)備片選信號,由主設(shè)備控制。

SPI主要特點(diǎn)有:可以同時(shí)發(fā)出和接收串行數(shù)據(jù);可以當(dāng)作主機(jī)或從機(jī)工作;提供頻率可編程時(shí)鐘;發(fā)送結(jié)束中斷標(biāo)志;寫沖突保護(hù);總線競爭保護(hù)等。

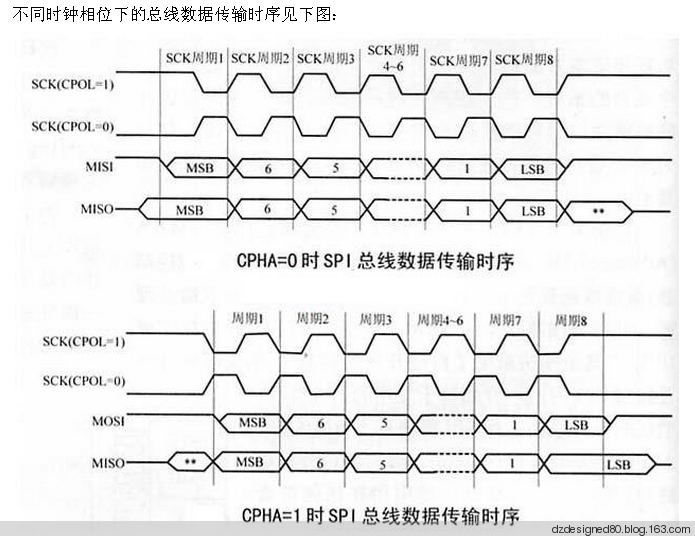

SPI總線四種工作方式 SPI 模塊為了和外設(shè)進(jìn)行數(shù)據(jù)交換,根據(jù)外設(shè)工作要求,其輸出串行同步時(shí)鐘極性和相位可以進(jìn)行配置,時(shí)鐘極性(CPOL)對傳輸協(xié)議沒有重大的影響。如果CPOL=0,串行同步時(shí)鐘的空閑狀態(tài)為低電平;如果CPOL=1,串行同步時(shí)鐘的空閑狀態(tài)為高電平。時(shí)鐘相位(CPHA)能夠配置用于選擇兩種不同的傳輸協(xié)議之一進(jìn)行數(shù)據(jù)傳輸。如果CPHA=0,在串行同步時(shí)鐘的第一個(gè)跳變沿(上升或下降)數(shù)據(jù)被采樣;如果CPHA=1,在串行同步時(shí)鐘的第二個(gè)跳變沿(上升或下降)數(shù)據(jù)被采樣。SPI主模塊和與之通信的外設(shè)備時(shí)鐘相位和極性應(yīng)該一致。

從選擇(NSS)腳管理

有2種NSS模式:

圖211● 軟件NSS模式:可以通過設(shè)置SPI_CR1寄存器的SSM位來使能這種模式(見)。在這種模式下NSS引腳可以用作它用,而內(nèi)部NSS信號電平可以通過寫SPI_CR1的SSI位來驅(qū)動(dòng)

● 硬件NSS模式,分兩種情況:

─ NSS輸出被使能:當(dāng)STM32F10xxx工作為主SPI,并且NSS輸出已經(jīng)通過SPI_CR2寄存器的SSOE位使能,這時(shí)NSS引腳被拉低,所有NSS引腳與這個(gè)主SPI的NSS引腳相連并配置為硬件NSS的SPI設(shè)備,將自動(dòng)變成從SPI設(shè)備。 當(dāng)一個(gè)SPI設(shè)備需要發(fā)送廣播數(shù)據(jù),它必須拉低NSS信號,以通知所有其它的設(shè)備它是主設(shè)備;如果它不能拉低NSS,這意味著總線上有另外一個(gè)主設(shè)備在通信,這時(shí)將產(chǎn)生一個(gè)硬件失敗錯(cuò)誤(Hard Fault)。

─ NSS輸出被關(guān)閉:允許操作于多主環(huán)境。

● NSS:從設(shè)備選擇。這是一個(gè)可選的引腳,用來選擇主/從設(shè)備。它的功能是用來作為“片選引腳”,讓主設(shè)備可以單獨(dú)地與特定從設(shè)備通訊,避免數(shù)據(jù)線上的沖突。從設(shè)備的NSS引腳可以由主設(shè)備的一個(gè)標(biāo)準(zhǔn)I/O引腳來驅(qū)動(dòng)。一旦被使能(SSOE位),NSS引腳也可以作為輸出引腳,并在SPI處于主模式時(shí)拉低;此時(shí),所有的SPI設(shè)備,如果它們的NSS引腳連接到主設(shè)備的NSS引腳,則會(huì)檢測到低電平,如果它們被設(shè)置為NSS硬件模式,就會(huì)自動(dòng)進(jìn)入從設(shè)備狀態(tài)。當(dāng)配置為主設(shè)備、NSS配置為輸入引腳(MSTR=1,SSOE=0)時(shí),如果NSS被拉低,則這個(gè)SPI設(shè)備進(jìn)入主模式失敗狀態(tài):即MSTR位被自動(dòng)清除,此設(shè)備進(jìn)入從模式

評論