MSP430 Value Line MCU學(xué)習(xí)筆記 - 基礎(chǔ)時鐘模塊

由于要使用仿真器調(diào)試,加斷點(diǎn)后MCU被掛起,會導(dǎo)致看門狗被觸發(fā)而將MCU復(fù)位。因此在調(diào)試階段,我們需要先關(guān)閉看門狗。關(guān)閉看門狗的方法是:

WDTCTL = WDTPW + WDTHOLD;

WDTCTL是一個16位的寄存器,顧名思義,就是看門狗的控制寄存器。WDTHOLD是控制看門狗開關(guān)的標(biāo)志位。給WDTHOLD置位即關(guān)閉看門狗。但是這個WDTPW是什么呢?查手冊得知WDTPW是看門狗的密碼,這是一個宏,被定義為了0x5A00,這個密碼是干什么用的呢?原來,WDTCTL寄存器是一個非常特殊的寄存器,為了防止程序異常時意外關(guān)閉看門狗,對它進(jìn)行賦值操作時必須將其新值的高8位設(shè)為0x5A這個特定的值,也就是“密碼”。如果賦值時新值的高8位不是0x5A,會導(dǎo)致MCU立即被復(fù)位。總之,對WDTCTL進(jìn)行任何修改操作時,都要加上WDTPW的值。

2. 時鐘系統(tǒng)

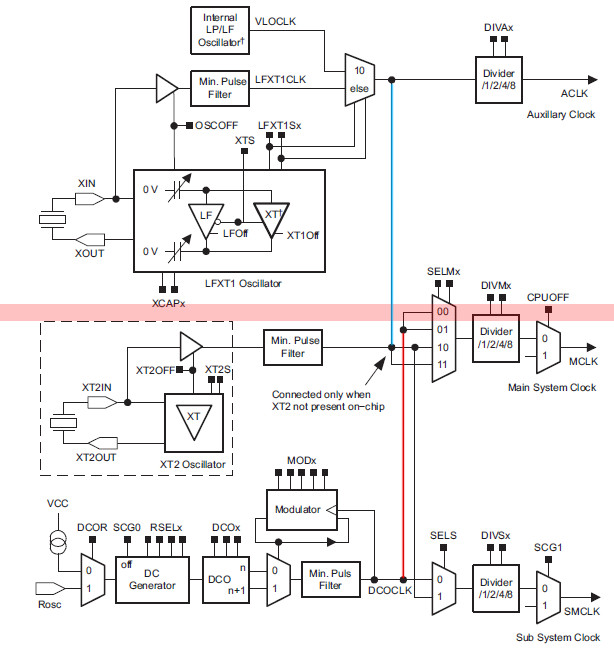

對于玩51單片機(jī)的人來說,學(xué)習(xí)MSP430的時鐘系統(tǒng)是很痛苦的,也很顛覆的。MSP430為了做到超低功耗,對時鐘系統(tǒng)進(jìn)行了精妙的設(shè)計(jì)。網(wǎng)上有文章專門講解MSP430的時鐘系統(tǒng),還有生動的配圖。但遺憾的是這些講解都多多少少的存在問題甚至是錯誤的。既然說人家講得不好,我也就斗膽說說自己的理解。對時鐘系統(tǒng)最精確的描述當(dāng)然就是手冊里的框圖了:

我不喜歡看這種框圖,覺得特別復(fù)雜,看起來累。但是靜下心來看它時,你會發(fā)現(xiàn)其實(shí)它并不是那么復(fù)雜,很多困惑的問題也就迎刃而解了。唯一需要你了解的背景知識是,你必須要認(rèn)識啥是多路選擇器(Mux)。。。

首先,MSP430的時鐘系統(tǒng)有這么幾個概念。

時鐘源:產(chǎn)生震蕩的時鐘信號。MSP430中最多有4個時鐘源,分別是:DCO(數(shù)控晶振),VLO(超低功耗低頻晶振),LFXT1(低頻外部晶振),XT2(高頻外部晶振)。在Value Line產(chǎn)品中,并非支持全部的四種時鐘源。以MSP430G2231為例,內(nèi)置了DCO和VLO,XT1可以自己焊接,XT2不支持。

時鐘:供系統(tǒng)設(shè)備使用的時鐘信號,通常是時鐘源的原始信號經(jīng)過分頻后得到。MSP430有3個時鐘,分別是:MCLK(主時鐘,供CPU核心使用),ACLK(輔助時鐘,供外圍設(shè)備使用),SMCLK(子系統(tǒng)時鐘,供外圍設(shè)備使用)。

每個時鐘都可以配置(1)從指定的時鐘源獲得信號 (2)對信號進(jìn)行/1/2/4/8分頻 (3)時鐘開關(guān)

上面的框圖我們從中間橫向的紅線分開看,上面一部分是低頻時鐘,LFXT1Sx這兩個標(biāo)志位用于選擇使用哪個時鐘源來驅(qū)動系統(tǒng)的低頻時鐘。藍(lán)色的線就是低頻時鐘源的輸出。下面一部分是高頻時鐘,紅色的細(xì)線是高頻時鐘的輸出(對沒有XT2的芯片來說)。需要注意的是,這條藍(lán)色線接在LFXT1Sx對應(yīng)的數(shù)據(jù)選擇器的后面。也就是說,系統(tǒng)只能選擇一個低頻時鐘。比如我選擇VLO作為ACLK的時鐘源,那藍(lán)色那條線上就是VLO的時鐘信號。那即使我有外部晶振,也不能選擇LFXT1作為MCLK的時鐘源。就是這種機(jī)制,很多人沒有理解清楚(或者沒有表達(dá)清楚),致使網(wǎng)上的大部分教程都在說,MCLK是從ACLK和DCO中二選一,這樣說是不準(zhǔn)確的。因?yàn)樗{(lán)色的線在ACLK的分頻器之前,所以并不受ACLK分頻設(shè)置的影響,因此藍(lán)色線上跑的并不是ACLK時鐘信號,而是ACLK的時鐘源信號。

更準(zhǔn)確的理解是這樣的:MCLK仍然是從DCO、VLO、LFXT1和XT2(如果有的話)中四選一,ACLK仍然是從LFXT1和VLO中二選一,SMCLK仍然可以從DCO和XT2(如果有的話)中二選一(如果沒有XT2就在DCO、LFXT1、VLO中三選一)。只不過有一個約束,那就是如果MCLK或者SMCLK想要選擇VLO或者LFXT1,那就必須跟ACLK選的一樣。

在絕大部分Value Line產(chǎn)品中(以MSP430G2231為例),你可以采用更簡單的記法:低頻時鐘源從LFXT1和VLO中選一個,高頻時鐘源只有DCO一個。因此對系統(tǒng)時鐘(MCLK, ACLK, SMCLK)來說,只有2個時鐘源,一個低頻一個高頻。三個系統(tǒng)時鐘都可以選擇使用低頻時鐘源(圖中藍(lán)線)或者高頻時鐘源(圖中紅線)。(2012年7月11日勘誤:MCLK和SMCLK可以從低頻和高頻中選一個,而ACLK只能選擇低頻)

---------以下內(nèi)容均以MSP430G2231和MSP430G2553芯片為例,即不存在XT2---------

3. 具體編程,對時鐘源和系統(tǒng)時鐘的配置和使用

(1)低頻時鐘源配置——寄存器BCSCTL3 (Basic Clock System Control Register 3)

配置低頻時鐘的時鐘源其實(shí)就是修改上面圖中的LFXT1Sx,這兩個標(biāo)志位位于BCSCTL3這個8位寄存器的第4、5位。

//使用頻率約為12kHz的VLO作為低頻時鐘源

BCSCTL3 |= LFXT1S_2;

頭文件中定義了LFXT1S_2,其實(shí)就是第4位為1,第5位為0. 含義是使用VLO

// 使用Launchpad自帶的32768Hz外部晶振,電容12.5pF

BCSCTL3 |= LFXT1S_0 + XCAP_3;

頭文件中定義的LFXTS_0含義是使用外部晶振,同時設(shè)置XCAP_3,含義是晶振的負(fù)載電容是12.5pF

----------------------------待續(xù),,,下面的還沒寫完------------------------------

(2)高頻時鐘源的配置——

(3)系統(tǒng)時鐘MCLK的時鐘源選擇——寄存器BCSCTL2 (Basic Clock System Control Register 2)

// 清晶振錯誤標(biāo)志位

IFG1 &= ~OFIFG;

// 不懂。。。

__bis_SR_register(SCG1 + SCG0);

//系統(tǒng)時鐘選擇為低頻,/8分頻

BCSCTL2 |= SELM_3 + DIVM_3;

評論