51手記之MEGAWIN

1.基本特性

工作頻率:24MHZ(最大,外部晶體)

有兩種節(jié)能模式和8位的系統(tǒng)時鐘分頻器。 時鐘源:外部晶體/時鐘,內(nèi)部高頻/低頻RC振蕩器;上電后,內(nèi)部高頻RC振蕩器(12MHZ)為默認(rèn)的系統(tǒng)時鐘源。軟件能使能其它振蕩器電路和通過編程AUXRA寄存器對它們進(jìn)行切換。切換時鐘源為外部晶體時,必須使能外部晶體振蕩器電路并等它穩(wěn)定后再切換。選好時鐘后,可軟件禁止未用的振蕩器電路以減少能耗。

切換系統(tǒng)時鐘為外部時鐘:

1).使能外部時鐘

IFMT=0X07;//AUXRA讀操作

SCMD=0X46;

SCMD=0XB9;//此時IFD的值=AUXRA的值

IFD |= 0X08;//設(shè)置使能外部晶體,將AUXRA的預(yù)設(shè)值寫入IFD

IFMT=0X06;//AUXRA寫操作

SCMD=0X46;

SCMD=0XB9;

2).切換到外部時鐘

IFMT=0X07;

SCMD=0X46;

SCMD=0XB9;

IFD |= 0X03;//設(shè)置外部晶體為系統(tǒng)時鐘

IFMT=0X06;

SCMD=0X46;

SCMD=0XB9;

3).關(guān)閉內(nèi)部時鐘

IFMT=0X07;

SCMD=0X46;

SCMD=0XB9;

IFD &= 0XFB;//設(shè)置將內(nèi)置晶體停止

IFMT=0X06;

SCMD=0X46;

SCMD=0XB9;

有六個復(fù)位源: 上電復(fù)位、WDT復(fù)位、軟件復(fù)位、外部(RST)復(fù)位、掉電檢測器(brown-out)復(fù)位及非法地址復(fù)位。

2.存儲器

1)程序存儲器

支持ISP(在系統(tǒng)可編程)/IAP(在應(yīng)用可編程);IAP空間可用作數(shù)據(jù)閃存。

IAP區(qū)域由IAPLB和ISP起始地址共同決定:IAP低邊界 = IAPLB * 256;IAP高邊界 = ISP起始地址 – 1;IAP低邊界地址必須不要高于ISP起始地址或非設(shè)備定義的空間。否則,可能會導(dǎo)致Flash存儲器中數(shù)據(jù)內(nèi)容遭到破壞。

2)數(shù)據(jù)存儲器

片上256字節(jié)隨機(jī)存取儲存器和1024字節(jié)片上擴(kuò)展存儲器(XRAM)

3.通用I/O口

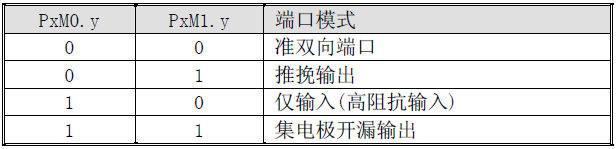

有41個普通I/O口(GPIO),P0, P1, P2, P3, P4(P40-P46)能被配置為準(zhǔn)雙向口、上拉輸出、集電極開漏輸出以及高阻輸入,P6.0 和 P6.1 僅可作準(zhǔn)雙向口模式及復(fù)用為 XTAL2和 XTAL1。每個端口有兩個模式寄存器來選擇各端口引腳的輸出類型:

4.中斷系統(tǒng)

有四級中斷優(yōu)先級的14個中斷源。與這四級中斷有關(guān)聯(lián)的特殊功能寄存器有IE、 IP0L、 IP0H、EIE1、EIP1L、EIP1H及XICON。

nINT0/nINT1 觸發(fā)類型:低電平或下降沿;

nINT2/nINT3觸發(fā)類型:低電平、下降沿、高電平或上升沿

5.定時器

三個16位定時/計(jì)數(shù)器:定時器 0、定時器1及定時器2;每一個包含兩個8位寄存器THx和TLx(這里,x=0、1或2)。它們可配置為定時器或事件計(jì)數(shù)器。三個定時器輸出口(T0CKO 對應(yīng)P34、T1CKO對應(yīng)P35、T2CKO對應(yīng)P10);T0/T1/T2時鐘可以選擇X12 模式。

定時器功能,TLx寄存器每12個系統(tǒng)時鐘周期(標(biāo)準(zhǔn)C51的機(jī)器周期)或每1個系統(tǒng)時鐘周期(是標(biāo)準(zhǔn)C51的12倍)加1,通過軟件設(shè)置AUXR2.T0X12、 AUXR2.T1X12和 T2MOD.T2X12位來選擇 。每12個系統(tǒng)時鐘周期加一,計(jì)數(shù)速率是1/12的晶振頻率。

計(jì)數(shù)器功能,根據(jù)對應(yīng)的外部輸入引腳的下降沿T0、T1或T2寄存器加1。在這功能中,每個定時器時鐘周期對外部輸入信號(T0、T1和T2引腳)進(jìn)行采樣,當(dāng)采樣信號出現(xiàn)一個高電平接著一個低電平,計(jì)數(shù)加1。當(dāng)檢測到跳變時新計(jì)數(shù)值出現(xiàn)在寄存器中。

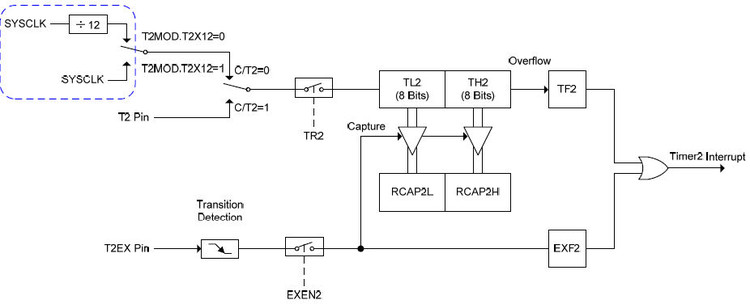

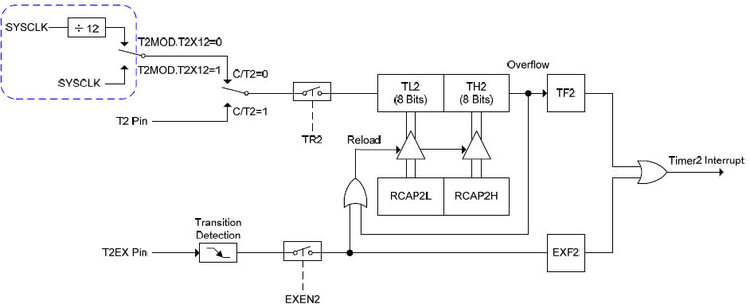

定時器2有四種工作模式:捕獲、自動加載(向上或向下計(jì)數(shù))、波特率發(fā)生器和可編程時鐘輸出,通過專用寄存器T2CON和T2MOD來選擇。

1)捕獲模式

2)自動加載模式

在復(fù)位之后,DCEN=0意思是默認(rèn)為定時器2向上計(jì)數(shù)。如果DCEN置位,定時器2向上或向下計(jì)數(shù)由T2EX引腳的值來決定。

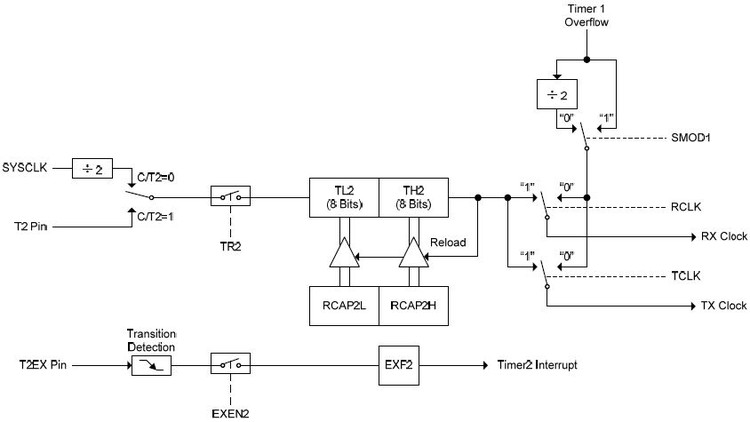

3)波特率發(fā)生器模式

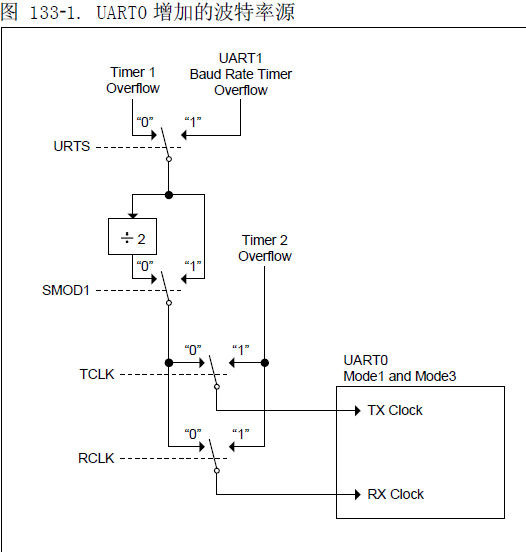

T2CON寄存器的RCLK和/或RCLK位允許串行口發(fā)送和接收波特率既可源自定時器1或定時器2。當(dāng)TCLK=0時,定時器1作為串行口傳送波特率發(fā)生器。當(dāng)TCLK=1,定時器2作為串行口傳送波特率發(fā)生器。RCLK對串行口接收波特率有相同的功能

4)可編程時鐘輸出模式

CP/RL2=0且T2OE=1;定時器2作為一個輸出占空比為50%的可編程時鐘發(fā)生器,所產(chǎn)生的時鐘從P1.0 引腳輸出來。

輸出頻率=Fosc/4(65536-(RCAP2H,RCAP2L))

定時器2 的可編程時鐘輸出模式編程步驟如下:

a.置位T2MOD寄存器的T2OE位。 b.清除T2CON寄存器的C/T2位。

c.從公式計(jì)算出16位加載值并輸入到RCAP2H和RCAP2L寄存器。

d.在TH2和TL2輸入一個16位初始值??梢院椭剌d值相等。

e.設(shè)置T2CON的TR2控制位開啟動定時器。

在時鐘輸出模式,定時器2翻轉(zhuǎn)不會產(chǎn)生中斷

6.串行口

2個全雙工串行口,功能同標(biāo)準(zhǔn)51;

串行口可以工作在四種模式:模式 0 提供同步通訊同時模式 1、2 和模式 3 提供異步通訊。異步通訊作為一個全雙工的通用異步收發(fā)器(UART),可以同時發(fā)送和接收并使用不同的波特率。

模式0:8位數(shù)據(jù)(低位先出)通過RXD0(P3.0)傳送和接收,波特率可通過SCFG寄存器的URM0X6位選擇為系統(tǒng)時鐘頻率的1/12或1/2。

模式1:10位數(shù)據(jù)通過TXD0傳送或通過RXD0接收,波特率是可變的。

模式2:11位數(shù)據(jù)通過TXD0傳送或通過RXD0接收,波特率可以配置為1/32或1/64 的系統(tǒng)時鐘頻率

模式3:11位數(shù)據(jù)通過TXD0傳送或通過RXD0接收,波特率是可變的。

除了標(biāo)準(zhǔn)操作外,UART0還能具有偵察丟失停止位的幀錯誤和自動地址識別的功能。

串口1使用獨(dú)立波特率發(fā)生器,串口0可選擇使用定時器1或定時器2(T2CON的RCLK和TCLK決定),也可共用串口1的波特率(RCLK=0,TCLK=0及URTS=1)

7.可編程計(jì)數(shù)器陣列(PCA)

該功能與標(biāo)準(zhǔn)定時/計(jì)數(shù)器相比以更少的CPU占用提供了更多的定時能力。它的優(yōu)點(diǎn)包括減少了軟件復(fù)雜度并提高了精度。

PCA由一個專用定時/計(jì)數(shù)器作為一個6組比較/捕獲模塊的時間基礎(chǔ),6組比較/捕獲模塊中的每一組都可以編程為如下任意模式:

- 上升和/或下降沿捕獲

- 軟件定時器

- 高速輸出

- 脈寬調(diào)制(PWM)輸出

1)PCA 定時器/計(jì)數(shù)器

它的時鐘輸入可以從以下來源選擇(CPS1 和 CPS0選擇):

- 1/12 系統(tǒng)時鐘頻率

- 1/2 系統(tǒng)時鐘頻率

- 定時器0溢出,可以讓低頻時鐘源輸入到PCA定時器

- 外部時鐘輸入,ECI(P1.1)引腳的1-0反轉(zhuǎn)

2)比較/捕獲模塊

6組比較/捕獲模塊中的每一組都有一個模式寄存器,叫做CCAPMn(n代表0,1,2,3,4,5),來選擇其工作模式。ECCFn位控制當(dāng)中斷標(biāo)志置位時每個模塊的中斷開啟/關(guān)閉。

3)PCA運(yùn)行模式

具體工作模式與STC同。

提供4種精度的PWM輸出:8位(可自動重載)、10位、12位、16位(后3種需手動重載溢出值)

8.串行外設(shè)接口(SPI)

提供了一個高速串行通訊接口(SPI)。SPI接口是一種全雙工、高速同步通訊總線,有兩種操作模式:主機(jī)模式和從機(jī)模式。無論哪種模式,12MHz系統(tǒng)時鐘時支持高達(dá)3Mbps的通訊速度。SPI狀態(tài)寄存器(SPSTAT)有一個傳送完成標(biāo)志(SPIF)和寫沖突標(biāo)志(WCOL)。

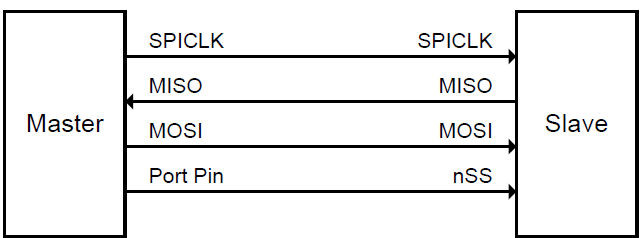

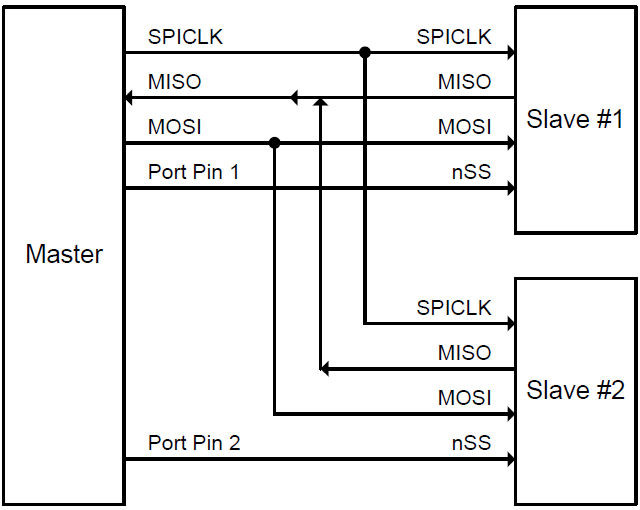

SPI接口有4個引腳:MISO (P1.6), MOSI (P1.5), SPICLK (P1.7) 和nSS (P1.4)。

1)典型SPI配置模式:

a.單主機(jī)單從機(jī)

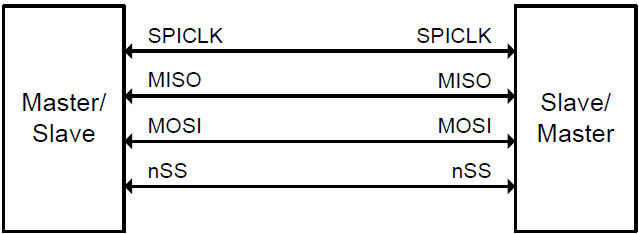

b.互為主機(jī)/從機(jī)

c.單主機(jī)多從機(jī)

2)注意事項(xiàng)

SPI通訊中,傳輸總是由主機(jī)發(fā)起 。若 SPI使能(SPEN=1)并作為主機(jī)運(yùn)行,寫入SPI數(shù)據(jù)寄存器(SPDAT) 數(shù)據(jù)即可啟動SPI時鐘生成器和數(shù)據(jù)傳輸器,大約半個到1個SPI位時間后寫入SPDAT的數(shù)據(jù)開始出現(xiàn)在MOSI線上。

在開始傳輸之前,主機(jī)通過拉低相應(yīng)nSS引腳選擇一個從機(jī)作為當(dāng)前從機(jī)。寫入SPDAT寄存器德數(shù)據(jù)從主機(jī)MOSI引腳移出,同時從從機(jī)MISO移入主機(jī)MISO的數(shù)據(jù)也寫入到主機(jī)的SPDAT寄存器中。移出1字節(jié)后,SPI時鐘發(fā)生器停止,置傳輸完成標(biāo)志SPIF,若SPI中斷使能則生成一個中斷。主機(jī)CPU和從機(jī)CPU中的兩個移位寄存器可以看成一個分開的16位環(huán)形移位寄存器,數(shù)據(jù)從主機(jī)移到從機(jī)同時數(shù)據(jù)也從從機(jī)移到主機(jī)。這意味著,在一次傳輸過程中,主從機(jī)數(shù)據(jù)進(jìn)行了交換。

SPI在發(fā)送方向是單緩沖的,而在接收方向是雙緩沖的。發(fā)送數(shù)據(jù)直到上一次數(shù)據(jù)發(fā)送完成后才能寫入移位寄存器,數(shù)據(jù)發(fā)送過程中寫入數(shù)據(jù)寄存器就會使WCOL(SPSTAT.6) 置位來表明數(shù)據(jù)沖突。這種情況下,正在發(fā)送的數(shù)據(jù)繼續(xù)發(fā)送,而剛寫入數(shù)據(jù)寄存器造成沖突的數(shù)據(jù)就會丟失。WCOL使用軟件向其位寫入’1’來清零。

SPI時鐘頻率選擇(主機(jī)模式)使用SPCTL寄存器的SPR1 和SPR0 位來設(shè)置。

9.鍵盤中斷

鍵盤中斷功能主要用于當(dāng)P2口等于或不等于某個值時產(chǎn)生一個中斷,這個功能可以用作總線地址識別或鍵盤鍵碼識別。

鍵盤中斷掩碼寄存器(KBMASK) 用來定義P2口哪些引腳可以產(chǎn)生中斷;鍵盤模式寄存器(KBPATN)用來定義與P2口值進(jìn)行比較的值,比較匹配時硬件置鍵盤中斷控制寄存器(KBCON)中的鍵盤中斷標(biāo)志(KBIF)。

10.10位模數(shù)轉(zhuǎn)換器ADC

ADC子系統(tǒng)由一個模擬多路器(AMUX)、一個200ksps、10逐次逼近型模數(shù)轉(zhuǎn)換器組成。ADC轉(zhuǎn)換時鐘由ADCON寄存器的SPEED1、SPEED0兩位決定的系統(tǒng)時鐘分頻而來。(備注:目前建議ADC操作時,系統(tǒng)時鐘不要超過20MHz) ADC轉(zhuǎn)換結(jié)果=Vin*1024/Vdd;

在使用ACD功能之前,用戶應(yīng):

a.設(shè)置ADCEN 位啟動ADC硬件;

b.設(shè)置SPEED1 和 SPEED0位設(shè)定轉(zhuǎn)換速度;

c.設(shè)置CHS2、CHS1 和CHS0選擇輸入通道;

d.設(shè)置P1M0和P1M1寄存器將所選引腳設(shè)定成只輸入模式;

e.設(shè)置ADRJ 位配置ADC轉(zhuǎn)換結(jié)果輸出形式。

一旦轉(zhuǎn)換結(jié)束,硬件自動清除ADCS位,設(shè)置中斷標(biāo)志ADCI,并將轉(zhuǎn)換結(jié)果按照ADRJ的設(shè)置存入ADCH和ADCL。為了獲得最佳轉(zhuǎn)換效果,用作ADC的引腳應(yīng)當(dāng)禁止其數(shù)字輸出和輸入,可以將引腳設(shè)為只輸入模式。

11.看門狗定時器WDT

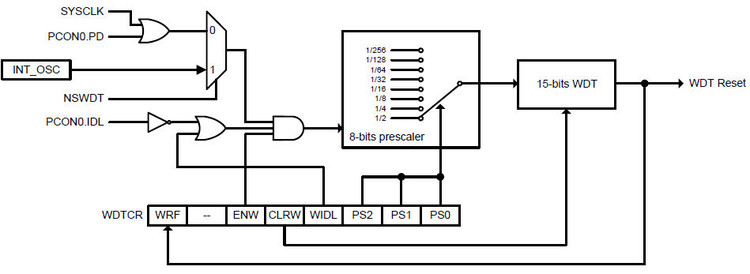

看門狗定時器 (WDT) 用來使程序從跑飛或死機(jī)狀態(tài)(諸如電源噪音/波動、靜電干擾等使CPU運(yùn)行出現(xiàn)混亂或死機(jī))恢復(fù)的一個手段。軟件跑飛時,WDT使系統(tǒng)復(fù)位來防止系統(tǒng)執(zhí)行錯誤的代碼。WDT由一個15位獨(dú)立定時器、一個8分頻器和一個控制寄存器(WDTCR)組成。

看門狗溢出時間=12*分頻值*32768/SYSCLK (系統(tǒng)時鐘為12Mhz時,最長延時8s,時鐘越高,延時越短)

評論