Eclipse開發(fā)調(diào)試ARM裸機(jī)程序(七)LCD

relocate:/* relocate U-Boot to RAM */

adrr0, _start/* r0 <- current position of code */

ldrr1, =TEXT_BASE/* test if we run from flash or RAM */

cmpr0, r1/* dont reloc during debug */

beqstack_setup

ldr sp, =1024*4 @ 設(shè)置堆棧

bl copy_to_ram_from_nand @ 到SDRAM中

注釋都沒(méi)有換,不過(guò)真心好用。完整的啟動(dòng)代碼如下:

@*

@ File:start.S

@ 功能:設(shè)置SDRAM,將程序到SDRAM,然后跳到SDRAM繼續(xù)執(zhí)行

@*

.equ MEM_CTL_BASE, 0x48000000

.equ TEXT_BASE, 0x33F80000

.text

.global _start

_start:

bl pre_lowlevel_init @ 關(guān)閉WATCHDOG,屏蔽中斷

bl system_clock_init

bl mem_ctrl_asm_init @ 設(shè)置存儲(chǔ)控制器

bl nand_asm_init

relocate:/* relocate U-Boot to RAM */

adrr0, _start/* r0 <- current position of code */

ldrr1, =TEXT_BASE/* test if we run from flash or RAM */

cmpr0, r1/* dont reloc during debug */

beqstack_setup

ldr sp, =1024*4 @ 設(shè)置堆棧

bl copy_to_ram_from_nand @ 到SDRAM中

stack_setup:

ldr sp, =0x33F80000 @ 設(shè)置堆棧

ldrpc, _start_armboot @ 跳到SDRAM中繼續(xù)執(zhí)行

_start_armboot:.word main

@stack_setup:

@ ldr sp, =1024*4 @ 設(shè)置堆棧

@ bl main

halt_loop:

b halt_loop

/*

* 板級(jí)初始化預(yù)處理函數(shù)

* 關(guān)看門狗、屏蔽中斷

*/

pre_lowlevel_init:

/* turn off the watchdog */

#define pWTCON0x53000000

#define INTMSK0x4A000008/* Interrupt-Controller base addresses */

#define INTSUBMSK0x4A00001C

#define CLKDIVN0x4C000014/* clock divisor register */

ldrr0, =pWTCON

movr1, #0x0

strr1, [r0]

/*

* mask all IRQs by setting all bits in the INTMR - default

*/

movr1, #0xffffffff

ldrr0, =INTMSK

strr1, [r0]

ldrr1, =0x7fff

ldrr0, =INTSUBMSK

strr1, [r0]

movpc, lr

/* end_of pre_lowlevel_init */

/*

* 系統(tǒng)時(shí)鐘初始化函數(shù)

* S3C2440: FCLK:HCLK:PCLK = 1:4:8(FCLK is 405 MHz)

*/

#define CLKDIVN0x4C000014

#define CLK_CTL_BASE0x4C000000

#define MDIV_4050x7f << 12

#define PSDIV_4050x21

#define MDIV MDIV_405

#define PSDIV PSDIV_405

#define CLKDIV 0x5 /* FCLK:HCLK:PCLK = 1:4:8 */

system_clock_init:

ldrr0, =CLKDIVN

movr1, #CLKDIV

strr1, [r0]

/*

* 設(shè)置arm920t為異步時(shí)鐘模式

*

* 復(fù)位時(shí),arm920t處于快速總線時(shí)鐘模式,該模式下

* core和AMBA都由BCLK控制,設(shè)置為異步模式后,core

* 由FCLK控制

*/

mrcp15, 0, r1, c1, c0, 0

orrr1, r1, #0xc0000000

mcrp15, 0, r1, c1, c0, 0

movr1, #CLK_CTL_BASE

movr2, #MDIV

addr2, r2, #PSDIV

strr2, [r1, #0x04]/* MPLLCON */

movpc, lr

/* end_of system_clock_init*/

/*

* NAND FLASH初始化函數(shù)

* TACLS:TWRPH0:TWRPH1 = 1:2:1, BUS_WIDTH_8

*/

#define S3C2440_NAND_BASE0x4E000000

#define NFCONF_OFFSET 0x0

#define NFCONT_OFFSET 0x4

nand_asm_init:

ldrr0, =S3C2440_NAND_BASE

ldrr1, =0x001210

str r1, [r0, #NFCONF_OFFSET]

movr1, #0x3

str r1, [r0, #NFCONT_OFFSET]

movpc, lr

/*end_of nand_asm_init*/

mem_ctrl_asm_init:

@ 設(shè)置存儲(chǔ)控制器以便使用SDRAM等外設(shè)

mov r1, #MEM_CTL_BASE @ 存儲(chǔ)控制器的13個(gè)寄存器的開始地址

adrl r2, mem_cfg_val @ 這13個(gè)值的起始存儲(chǔ)地址

add r3, r1, #52 @ 13*4 = 54

1:

ldr r4, [r2], #4 @ 讀取設(shè)置值,并讓r2加4

str r4, [r1], #4 @ 將此值寫入寄存器,并讓r1加4

cmp r1, r3 @ 判斷是否設(shè)置完所有13個(gè)寄存器

bne 1b @ 若沒(méi)有寫成,繼續(xù)

mov pc, lr @ 返回

.align 4

mem_cfg_val:

@ 存儲(chǔ)控制器13個(gè)寄存器的設(shè)置值

.long 0x22011110 @ BWSCON

.long 0x00000700 @ BANKCON0

.long 0x00000700 @ BANKCON1

.long 0x00000700 @ BANKCON2

.long 0x00000700 @ BANKCON3

.long 0x00000700 @ BANKCON4

.long 0x00000700 @ BANKCON5

.long 0x00018005 @ BANKCON6

.long 0x00018005 @ BANKCON7

.long 0x008C07A3 @ REFRESH

.long 0x000000B1 @ BANKSIZE

.long 0x00000030 @ MRSRB6

.long 0x00000030 @ MRSRB7

啟動(dòng)完就跳到了main那里出了。關(guān)于LCD的參數(shù)什么的就不多說(shuō)了,以前RVDS下的整個(gè)過(guò)來(lái)都沒(méi)有問(wèn)題。很多博客,教材上講的很清楚。這里主要寫寫實(shí)現(xiàn)過(guò)程。

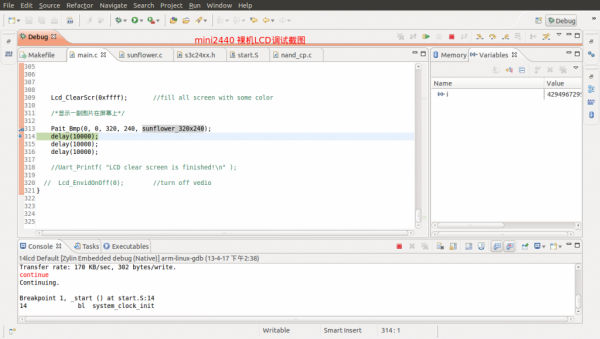

調(diào)試截圖:

顯示截圖:

代碼:http://download.csdn.net/detail/kangear/5268137

評(píng)論