GNU ARM匯編--(七)s3c2440的串口控制

還是從s3c2440的datasheet開始:

本文引用地址:http://www.ex-cimer.com/article/201611/321724.htms3c2440A的UART提供3個獨(dú)立的異步串行IO口,每一個都支持中斷和DMA.換句話來說,UART可以產(chǎn)生中斷請求或DMA請求來在CPU和UART之間傳輸數(shù)據(jù).UART在系統(tǒng)時鐘下最高支持115200的波特率.如果使用UEXTCLK的話,UART可以工作在更高速的時鐘下.每個UART通道都有來年各個64字節(jié)的FIFO,一個是接收用的,一個是發(fā)送用的.

UART包括可編程的波特率,IR發(fā)送/接受,一或兩個停止位,5/6/7/8個數(shù)據(jù)位和奇偶校驗(yàn).

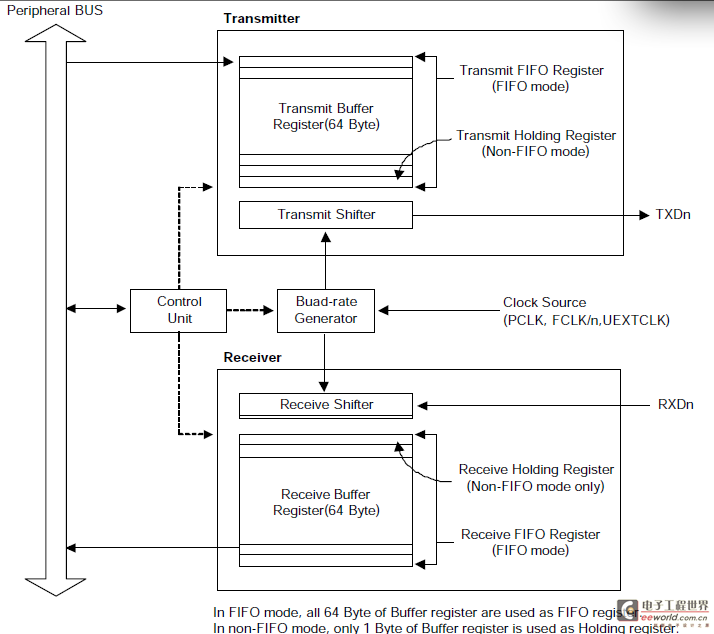

每個UART包括一個波特率產(chǎn)生器,發(fā)送器,接收器和一個控制單元.波特率產(chǎn)生器可以由PCLK FCLK/n 或者UEXTCLK來鎖定.發(fā)送器和接收器包含64字節(jié)的FIFO和數(shù)據(jù)移位器.數(shù)據(jù)首先寫到FIFO中,然后在發(fā)送之前復(fù)制到發(fā)送器的移位器.最后數(shù)據(jù)移位通過TxDn數(shù)據(jù)發(fā)送管腳發(fā)送出去.同樣的,接收的數(shù)據(jù)通過RxDn接收數(shù)據(jù)管腳移位進(jìn)來,然后從移位器拷貝到FIFO中.

UART的框圖如下:

值得說的是:在FIFO模式下,buffer寄存器的所有64個字節(jié)都被用作FIFO寄存器.而在非FIFO模式下,buffer寄存器只有一個字節(jié)被用于Holding寄存器.

串口的操作:

串口操作包括如下:數(shù)據(jù)發(fā)送,數(shù)據(jù)接收,中斷產(chǎn)生,波特率產(chǎn)生,loopback模式,IR模式和自動流控制.

數(shù)據(jù)發(fā)送:

發(fā)送的數(shù)據(jù)幀是可編程的.它包括一個開始位,5到8個數(shù)據(jù)位,一個可選的校驗(yàn)位和1到2個停止位,這些都在ULCONn寄存器中控制.發(fā)送器可以產(chǎn)生終止條件,可以在一個數(shù)據(jù)幀的發(fā)送時間內(nèi)強(qiáng)制串口輸出為邏輯0.在當(dāng)前的傳輸數(shù)據(jù)發(fā)送完成后會發(fā)送一個終止信號,在終止信號發(fā)送后,它會繼續(xù)發(fā)送數(shù)據(jù)到Tx FIFO(而在非FIFO模式下是Tx holding寄存器).

數(shù)據(jù)接收:

和發(fā)送一樣,接收的數(shù)據(jù)幀也是可編程的.它包括一個開始位,5到8個數(shù)據(jù)位,一個可選的校驗(yàn)位和1到2個停止位(ULCONn中設(shè)置).接收器可以探測overrun錯誤parity錯誤frame錯誤和終止條件,每一個都會設(shè)置一個錯誤標(biāo)記.

overrun錯誤:在舊的數(shù)據(jù)被讀完之前新的數(shù)據(jù)覆蓋了舊的數(shù)據(jù)

parity錯誤:接收器探測到一個未知的校驗(yàn)條件

frame錯誤:接收數(shù)據(jù)沒有有效的停止位

終止條件:RxDn輸入在長于一個幀傳輸時間的期間內(nèi)保持為邏輯0

中斷/DMA請求產(chǎn)生

每個UART有7個狀態(tài)信號(Tx/Rx/error):overrun error,parity error,frame error,break,接收緩沖數(shù)據(jù)準(zhǔn)備,發(fā)送緩沖空和發(fā)送移位器空.所有都由對應(yīng)的UART狀態(tài)寄存器(UTRSTATn/UERSTATn)來指示.

overrun錯誤,parity錯誤,frame錯誤和終止條件都是接收錯誤狀態(tài).如果UCONn的接收錯誤狀態(tài)中斷使能位被置位,每一個錯誤都可以引起接收錯誤狀態(tài)中斷請求.當(dāng)一個接收錯誤狀態(tài)中斷請求被探測到,可以通過讀UERSTSTn來識別.

當(dāng)在FIFO模式下接收器將數(shù)據(jù)從接收器的移位器發(fā)送到接收器的FIFO寄存器,接收的數(shù)據(jù)達(dá)到了Rx FIFO的觸發(fā)線,Rx中斷產(chǎn)生.如果在控制寄存器(UCONn)接收模式被選為1(中斷請求或輪循模式).在非FIFO模式下,將數(shù)據(jù)從接收器的移位器發(fā)送到接收holding寄存器會引起Rx中斷(中斷請求和輪循模式下).

當(dāng)發(fā)送器從發(fā)送器的FIFO寄存器發(fā)送數(shù)據(jù)到移位寄存器時,發(fā)送器的FIFO中存留的數(shù)據(jù)數(shù)量小于Tx FIFO的觸發(fā)線時,Tx中斷產(chǎn)生,如果控制寄存器的發(fā)送模式被選為中斷請求或者輪循模式.在非FIFO模式下,在中斷請求和輪循模式下從發(fā)送器的Holding寄存器發(fā)送數(shù)據(jù)到發(fā)送器的移位器會引起Tx中斷.

如果控制寄存器的接收模式和發(fā)送模式選為DMA請求模式,在上面提到的條件下DMA請求會取代Tx或者Rx中斷請求.

UART錯誤狀態(tài)FIFO

UART除了有Rx FIFO寄存器外還有錯誤狀態(tài)FIFO.錯誤狀態(tài)FIFO會指明在FIFO寄存器中哪個數(shù)據(jù)在接收時是錯誤的.當(dāng)有錯的數(shù)據(jù)被讀出時,錯誤中斷就產(chǎn)生.為了清除錯誤狀態(tài)FIFO,有錯誤的URXHn和UERSTATn就必須被讀出.

波特率的產(chǎn)生:

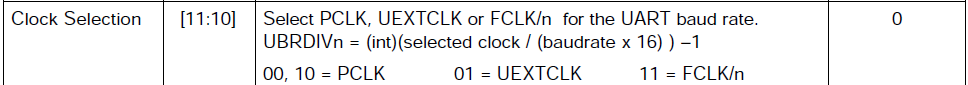

每個UART的波特率產(chǎn)生器為發(fā)送器和接收器提供特定的時鐘.波特率產(chǎn)生器的時鐘源可以選為內(nèi)部系統(tǒng)時鐘或者UEXTCLK.換句話說,被除數(shù)由UCONn寄存器的時鐘選擇確定.波特率的時鐘由源時鐘(PCLKFCLK/nUEXTCLK)除以16和UART波特率除數(shù)寄存器(UBRDIVn)中的16bit除數(shù).

公式如下:

UBRDIVn = (int)( UART clock / ( buad rate x 16) ) –1

( UART clock: PCLK, FCLK/n or UEXTCLK )

接下來看各個寄存器的描述:

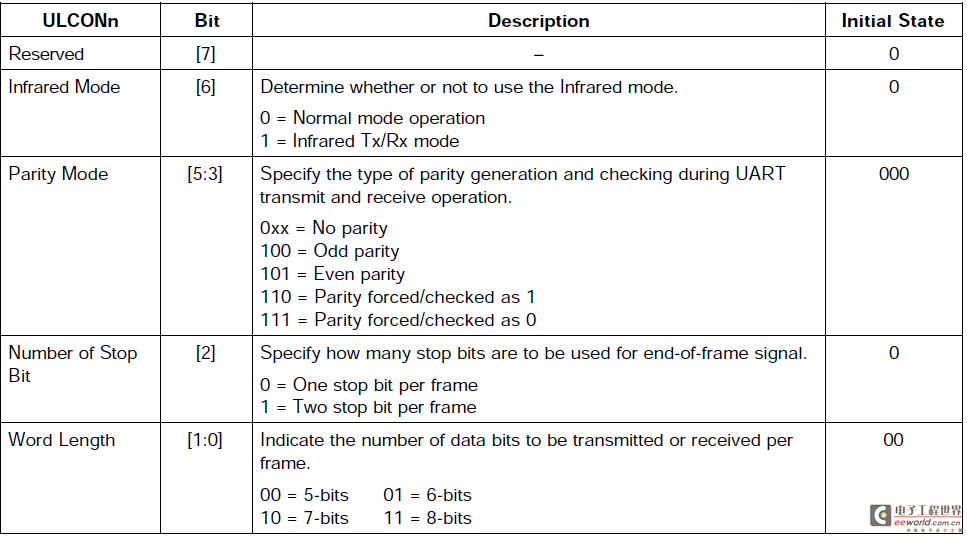

UART LINE CONTROL REGISTER

ULCONn用來配置每一幀數(shù)據(jù)的格式的:

根據(jù)上圖,配置如下:

IR mode[6] = 0(普通模式) Parity Mode[5:3] = 0xx(無校驗(yàn)) Number of Stop Bit[2] = 0(一個停止位)

word Length[1:0] = 11(8-bits)

UART CONTROL REGISTER

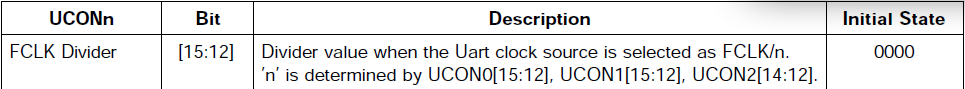

如果Uart的時鐘源用FCLK/n,那么FCLK Divider就是配置這個n的

這個地方就是配置Uart的時鐘源

Tx Interrupt Type [9] 中斷請求類型:0是Pulse 1是Level

Rx Interrupt Type [8] 中斷請求類型:0是Pulse 1是Level

Rx Time Out Enable [7] 在FIFO使能的情況下,是否打開Rx Time Out中斷 0是關(guān)閉 1是打開

Rx Error Status Interrupt Enable [6] 使能Uart對異常產(chǎn)生中斷,比如各種錯誤 0是關(guān)閉 1是打開

Loopback Mode [5] 回環(huán)模式 0是普通模式 1是回環(huán)模式

Send Break Signal [4] 是否發(fā)送終止信號 0是正常 1是發(fā)送終止信號

Transmit Mode [3:2] 決定使用哪種功能來寫數(shù)據(jù)到發(fā)送緩沖寄存器 01中斷請求或輪循模式

Receive Mode [3:2] 決定使用哪種功能來從接收緩沖寄存器讀數(shù)據(jù) 01中斷請求或輪循模式

UART FIFO CONTROL REGISTER

評論