51單片機-AT24C

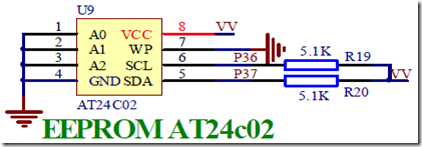

一般數(shù)字芯片都在左下角和右上角為GND,VCC。容量的計算方法:AT24Cxx :01"1024

容量 = xx * 1kbit。

寫入過程:

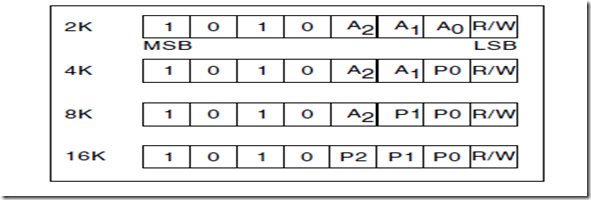

AT24C系列EEPROM芯片的固定部分為1010,A2,A1,A0引腳接高低電平后得到確定的3位編碼,形成7位編碼即為該器件的地址碼。

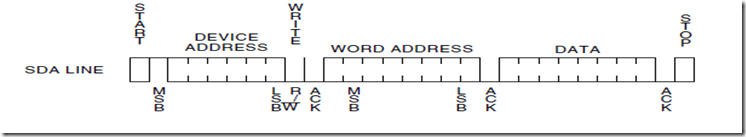

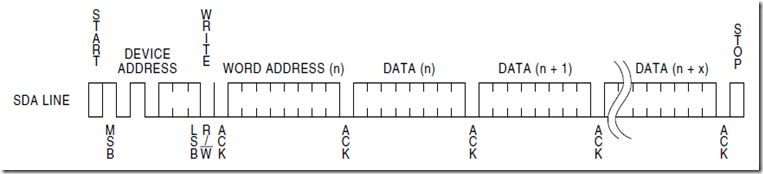

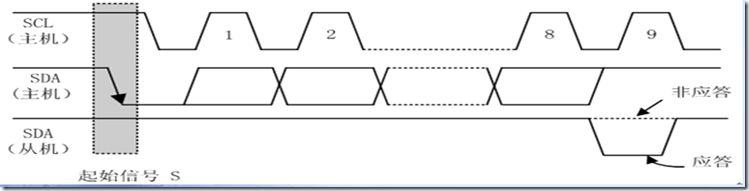

單片機進行寫操作時,首先發(fā)送該器件的7位地址碼和寫方向位”0”(共8位,即一個字節(jié)),發(fā)送完后釋放SDA線并在SCL線上產(chǎn)生第9個時鐘信號。被選中的存儲器器件在確認是自己的地址后,在SDA線上產(chǎn)生一個應答信號作為響應,單片機收到應答后就可以傳送數(shù)據(jù)了。傳送數(shù)據(jù)時,單片機首先發(fā)送一個字節(jié)的被寫入存儲器的首地址,收到存儲器器件的應答后,單片機就逐個發(fā)送數(shù)據(jù)字節(jié),但每發(fā)送一個字節(jié)后都要等待應答。AT24C系列片內(nèi)地址在接收到每一個數(shù)據(jù)字節(jié)地址后自動加1,在芯片的“一次裝載字節(jié)數(shù)”限度內(nèi),只需輸入首地址。裝載字節(jié)數(shù)超過芯片的“一次裝載字節(jié)數(shù)”時,數(shù)據(jù)地址將“上卷”,前面的數(shù)據(jù)將被覆蓋。

字節(jié)寫:

頁寫:

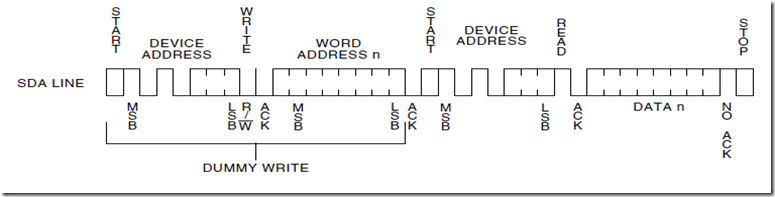

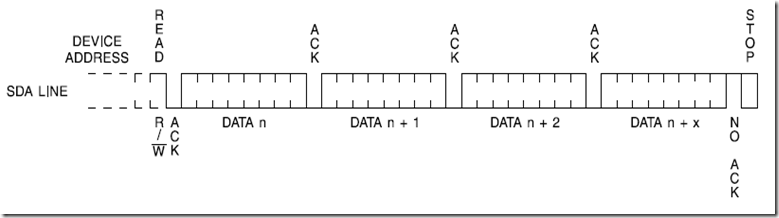

讀入過程:

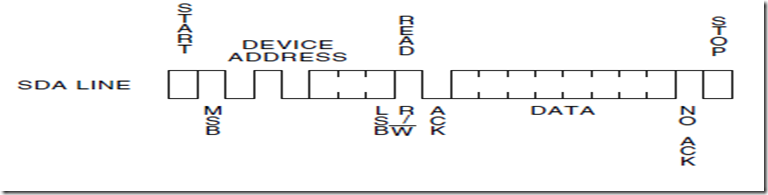

單片機先發(fā)送該器件的7位地址碼和寫方向位“0”(“偽寫”),發(fā)送完后釋放SDA線并在SCL線上產(chǎn)生第9個時鐘信號。被選中的存儲器器件在確認是自己的地址后,在SDA線上產(chǎn)生一個應答信號作為回應。

然后,再發(fā)一個字節(jié)的要讀出器件的存儲區(qū)的首地址,收到應答后,單片機要重復一次起始信號并發(fā)出器件地址和讀方向位(“1”),收到器件應答后就可以讀出數(shù)據(jù)字節(jié),每讀出一個字節(jié),單片機都要回復應答信號。當最后一個字節(jié)數(shù)據(jù)讀完后,單片機應返回以“非應答”(高電平),并發(fā)出終止信號以結(jié)束讀出操作。

當前地址讀:

隨機讀:

有序讀:

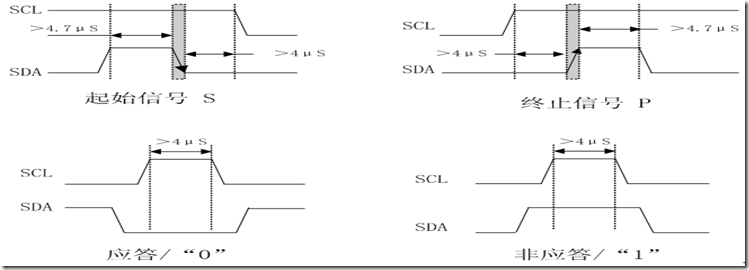

IIC總線模擬時序圖:

IIC總線應答時序圖:

設備地址:

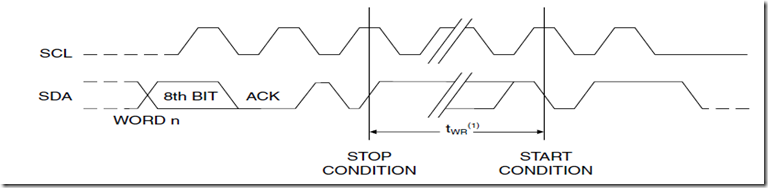

寫周期:

兩次寫之間要有一個10ms的twR間隔

關鍵詞:

51單片機AT24C數(shù)字芯

評論