FPGA在自定義測(cè)試中的四種應(yīng)用

而對(duì)于絕大多數(shù)測(cè)試與驗(yàn)證工程師來(lái)說,硬件自定義并非易事。幸運(yùn)的是,測(cè)試工程師也可以從摩爾定律中獲益。摩爾定律使CPU頻率得到不斷提高,從而使自定義測(cè)試系統(tǒng)的計(jì)算吞吐量也可不斷提升;另一方面,摩爾定律也正在推動(dòng)另一種計(jì)算器件—現(xiàn)場(chǎng)可編程門陣列(FPGA)的發(fā)展。FPGA本質(zhì)上是一種特殊的數(shù)字電路,用戶可以通過軟件編程的方式重新配置其硬件邏輯。FPGA不僅可以幫助工程師縮短測(cè)試時(shí)間,而且可以實(shí)現(xiàn)一些過去只能通過自定義硬件來(lái)實(shí)現(xiàn)的測(cè)試功能。下文就將介紹FPGA在測(cè)試系統(tǒng)中的四種典型應(yīng)用。

執(zhí)行實(shí)時(shí)連續(xù)的測(cè)量

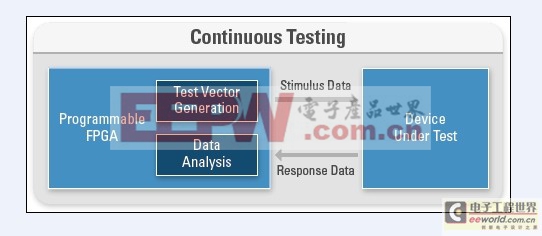

FPGA可以通過專享的硬件資源進(jìn)行處理數(shù)據(jù),從而實(shí)現(xiàn)較高的吞吐率,可以比通過I/O硬件先獲取數(shù)據(jù)再通過軟件執(zhí)行數(shù)據(jù)處理的速率更快。結(jié)合FPGA技術(shù)的測(cè)試系統(tǒng),不是按照傳統(tǒng)意義上的“采集、數(shù)據(jù)傳輸、后處理”模式,而是可以直接在I/O采集之后就直接在FPGA硬件上執(zhí)行數(shù)據(jù)處理,這種系統(tǒng)可以連續(xù)地測(cè)試被測(cè)設(shè)備,從而縮短測(cè)試時(shí)間。

通過FPGA上的專用硬件資源可以實(shí)現(xiàn)實(shí)時(shí)測(cè)量,如快速傅里葉變換(FFT)等?;贔PGA硬件本身所具有并行執(zhí)行特性,可以對(duì)多個(gè)輸入通道同時(shí)進(jìn)行測(cè)量,或者對(duì)單通道同時(shí)進(jìn)行多種計(jì)算參數(shù)的測(cè)量。

圖1:使用FPGA硬件生成測(cè)試向量,并對(duì)采集數(shù)據(jù)進(jìn)行實(shí)時(shí)連續(xù)分析

自定義觸發(fā)和采集

使用FPGA可以進(jìn)行連續(xù)的實(shí)時(shí)信號(hào)處理或數(shù)據(jù)計(jì)算,從而可以添加自定義觸發(fā)和數(shù)據(jù)記錄功能,從而有選擇地傳遞所需的數(shù)據(jù)。相對(duì)于只能執(zhí)行一組固定操作的傳統(tǒng)儀器,帶有FPGA儀器的可重置特性可以滿足特定的硬件應(yīng)用需求。

例如,頻域觸發(fā)應(yīng)用就體現(xiàn)了FPGA可重置特性的優(yōu)勢(shì)。有些傳統(tǒng)頻譜分析儀可以使用頻率觸發(fā)功能,但不能實(shí)時(shí)進(jìn)行。另一方面,矢量信號(hào)分析儀(VSA)可進(jìn)行實(shí)時(shí)功率觸發(fā),但不能實(shí)時(shí)地選擇感興趣的頻率信號(hào)。通過將FPGA技術(shù)添加到矢量信號(hào)分析儀中,您可以創(chuàng)建一個(gè)實(shí)時(shí)的、頻率相關(guān)的觸發(fā)功能,或者可以根據(jù)需要執(zhí)行其他自定義的觸發(fā)操作。

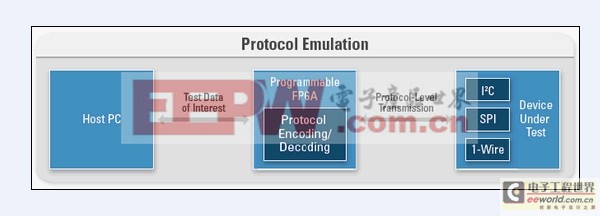

自定義協(xié)議接口

FPGA可以直接在硬件上對(duì)數(shù)據(jù)進(jìn)行編解碼,而無(wú)需使用軟件將信號(hào)信息編碼成協(xié)議信號(hào)(或?qū)f(xié)議信號(hào)解碼成信號(hào)信息)。這樣就可以幫助簡(jiǎn)化測(cè)試系統(tǒng)軟件,因?yàn)橄到y(tǒng)軟件只需要處理信號(hào)信息,使得協(xié)議級(jí)通信變得可行。而在過去,在只有預(yù)定義測(cè)試向量的情況下,是不適合通過軟件進(jìn)行帶有協(xié)議通訊的測(cè)試的(例如,當(dāng)基于協(xié)議數(shù)據(jù)需要快速?zèng)Q策時(shí))。FPGA對(duì)于那些從接收到發(fā)送數(shù)據(jù)間需要快速響應(yīng)的應(yīng)用也是有必要的,在這種情形下,測(cè)試硬件必須能夠快速檢測(cè)和響應(yīng)。

因?yàn)镕PGA是可通過軟件進(jìn)行重配置的硬件資源,因此對(duì)于同一硬件,可以通過不同配置支持多種協(xié)議,從而促進(jìn)硬件的重復(fù)使用。此外,還可以利用FPGA的硬件級(jí)執(zhí)行性能實(shí)現(xiàn)復(fù)雜的協(xié)議狀態(tài)機(jī),此外基于FPGA的并行執(zhí)行特性,可以實(shí)現(xiàn)同一協(xié)議接口的多個(gè)實(shí)例,從而進(jìn)行多個(gè)被測(cè)設(shè)備的并行測(cè)試。

閉環(huán)控制和動(dòng)態(tài)測(cè)試

如今有許多被測(cè)設(shè)備需要與測(cè)試環(huán)境進(jìn)行實(shí)時(shí)的信號(hào)交互,在這種情況下,如果測(cè)試系統(tǒng)不能對(duì)被測(cè)設(shè)備提供實(shí)時(shí)反饋信息,就可能無(wú)法提供足夠的測(cè)試覆蓋范圍。例如,現(xiàn)代通信方案通常包含確認(rèn)數(shù)據(jù)包或比特?cái)?shù)據(jù)。如果測(cè)試系統(tǒng)不能準(zhǔn)確地解析這些確認(rèn)數(shù)據(jù)包或比特,并及時(shí)作出響應(yīng),那么可能無(wú)法正確地測(cè)試被測(cè)設(shè)備。在大多數(shù)情況下,只有硬件(FPGA)可以提供這種低延遲響應(yīng)。

另一個(gè)實(shí)例是硬件在環(huán)(HIL)測(cè)試系統(tǒng)。在HIL系統(tǒng)中,待測(cè)設(shè)備通常是控制器,而測(cè)試系統(tǒng)必須模擬被控對(duì)象的行為。這樣可以提高對(duì)控制器進(jìn)行測(cè)試的性能和可靠性;在某些情況下,還可以在被控對(duì)象生產(chǎn)出來(lái)之前先通過測(cè)試系統(tǒng)模擬被控對(duì)象,從而對(duì)控制器的功能進(jìn)行驗(yàn)證。FPGA的高性能和低延遲可以基于確定性的閉環(huán)循環(huán)周期來(lái)準(zhǔn)確地模擬被控對(duì)象的行為。

圖2:FPGA硬件可以對(duì)協(xié)議級(jí)通信進(jìn)行編碼和解碼,從而簡(jiǎn)化測(cè)試系統(tǒng)軟件

評(píng)論