TIPGA450-Q1超聲波汽車倒車解決方案

The PGA450-Q1 is a fully integrated interface device for ultrasonic transducers used in automotive park distance or object detection applications. It incorporates these system blocks: voltage regulators, a 12-bit SAR ADC, an 8-bit microcontroller, a digital band-pass filter, a DAC, dual NMOS low-side drivers, a low-noise amplifier, an oscillator, and a LIN 2.1 physical interface and protocol for interfacing.

The PGA450-Q1 possesses an 8-bit microcontroller and OTP memory for program storage for processing the echo signal and calculating the distance between the transducer and the object. This data is transmitted through the LIN 2.1 communication protocol. The LIN 2.1 physical layer is slave-only and does not implement the LIN wake-up feature.

PGA450-Q1主要特性:

Dual NMOS Low-Side Drivers

Configurable Burst Generator

Low-Noise Amplifier

12-Bit SAR ADC

Configurable Digital Band-Pass Filter

Digital Signal Envelope Detect

On-Chip 8-Bit Microprocessor

LIN 2.1 Physical Interface and Protocol

Watchdog Timer

Four-Wire SPI for Testability / Programming

8K Bytes OTP

768 Bytes of FIFO RAM

256 Bytes Scratchpad RAM

8K Bytes of Development RAM

32 Bytes of EEPROM for Application

PGA450-Q1應(yīng)用:

Automotive Park Distance

Blind Spot Detection

Object Detection Applications

圖1.PGA450-Q1功能方框圖

The digital data path has the following components:

? Band-pass filter

? Rectifier

? Peak extractor

? Downsampler

? Low-pass filter

圖2.PGA450-Q1數(shù)字?jǐn)?shù)據(jù)通路方框圖

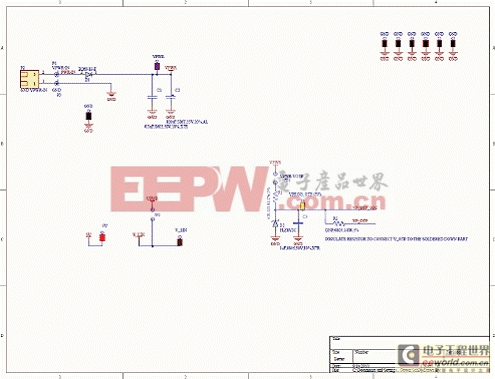

圖3.PGA450-Q1應(yīng)用電路圖

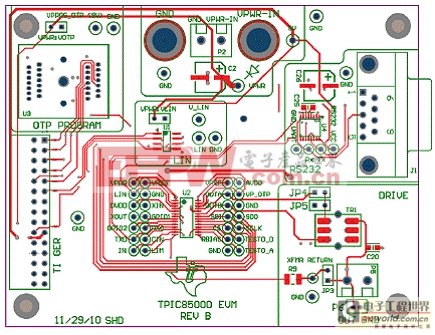

評估板PGA450-Q1 EVM

This user’s guide describes the characteristics, operation, and use of the PGA450-Q1 EVM.

評估板PGA450-Q1 EVM主要特性:

? Single power-supply input for basic operation

? Example single-ended transformer and 58-kHz transducer

? LIN master transceiver

? RS-232 transceiver for UART testing and debug

? PC control with a graphical user interface and USB communications board

圖4.評估板PGA450-Q1 EVM外形圖

圖5.評估板PGA450-Q1 EVM電路圖:LIN

圖6.評估板PGA450-Q1 EVM電路圖:電源

圖7.評估板PGA450-Q1 EVM電路圖:RS232

圖8.評估板PGA450-Q1 EVM電路圖:USB控制器

圖9.評估板PGA450-Q1 EVM電路圖: PGA450-Q1

圖10.評估板PGA450-Q1 EVM PCB布局圖:頂層

圖11.評估板PGA450-Q1 EVM PCB布局圖:底層

詳情請見:

http://www.ti.com/lit/ds/symlink/pga450-q1.pdf

和

http://www.ti.com/lit/ug/sldu007/sldu007.pdf

評論