基于DSP的視頻監(jiān)控系統(tǒng)的硬件設(shè)計

1 引言

本文引用地址:http://www.ex-cimer.com/article/257244.htm 目前視頻監(jiān)控廣泛應(yīng)用于安防監(jiān)控、工業(yè)監(jiān)控和交通監(jiān)控等領(lǐng)域。視頻監(jiān)控系統(tǒng)大致經(jīng)歷3個階段:首先是基于模擬信號的電視監(jiān)控系統(tǒng),其功能單一、易受干擾且不易擴(kuò)展;隨后出現(xiàn)基于PC機(jī)的圖像監(jiān)控系統(tǒng),其終端功能較強(qiáng).但價格昂貴,穩(wěn)定性差;近年來,隨著嵌入式技術(shù)成熟,嵌入式視頻采集處理系統(tǒng)具有可靠性高、速度快、成本低、體積小、功耗低、環(huán)境適應(yīng)性強(qiáng)等優(yōu)點(diǎn)。

基于嵌入式系統(tǒng)的上述諸多優(yōu)點(diǎn),這里提出一種基于DSP的視頻監(jiān)控系統(tǒng)解決方案。

2 系統(tǒng)硬件設(shè)計

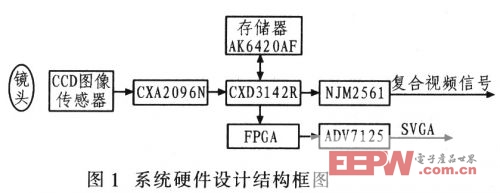

2.1 系統(tǒng)整體硬件結(jié)構(gòu)

整個系統(tǒng)硬件設(shè)計由電源、視頻信號處理、FPGA和外圍接口等模塊組成。其中,圖像處理模塊接收CCD圖像傳感器傳送的模擬視頻信號,并把模擬視頻信號模數(shù)轉(zhuǎn)換成數(shù)字信號,由DSP處理所轉(zhuǎn)換的數(shù)字信號,再轉(zhuǎn)換為標(biāo)準(zhǔn)的YUV 4:2:2格式的數(shù)字視頻信號,并將獲得的數(shù)字視頻信號送至FPGA模塊,對YUV數(shù)字信號進(jìn)行處理,從而產(chǎn)生標(biāo)準(zhǔn)的SVGA格式,幀頻為60 Hz的行、場同步信號。圖1為該系統(tǒng)硬件設(shè)計框圖。

2.2 電源模塊

電源模塊將外部輸入的12 V直流電源轉(zhuǎn)換成系統(tǒng)各模塊所需工作電壓。CCD圖像傳感器所需電壓為15 V和-7 V,DSP所需電壓為3.3 V和5 V,F(xiàn)PGA所需電壓為1.2 V、2.5 V和3.3 V。本設(shè)計采用MOTOROLA公司的DC-DC電源轉(zhuǎn)換器,MC34063A將12 V直流電壓轉(zhuǎn)換成5 V直流電壓,選用Texas Instruments公司的電源轉(zhuǎn)換器TPS75003將5 V直壓電源轉(zhuǎn)換成1.2 V、2.5 V和3.3 V直流電壓。而CCD圖像傳感器的工作電壓則由NE555和78L15產(chǎn)生。

2. 3 圖像處理模塊

2.3.1 圖像采集

本設(shè)計圖像采集電路將CCD傳感器輸出的模擬視頻信號轉(zhuǎn)換成離散的模擬視頻信號,再對模擬信號進(jìn)行相關(guān)雙采樣、自動增益控制處理后,傳輸至DSP轉(zhuǎn)換為數(shù)字信號。具體工作流程:系統(tǒng)上電復(fù)位后,DSP(CXD3142)產(chǎn)生控制信號驅(qū)動CCD圖像傳感器,把光信號轉(zhuǎn)換成PAL制式的模擬視頻信號,并把該信號輸入到CXA2096N的引腳DIN和PIN引腳。此時,在引腳SHD和SHP的控制下對輸入信號進(jìn)行相關(guān)雙采樣。當(dāng)SHD信號的下降沿到來時,采樣DIN信號電平,當(dāng)SHP信號的下降沿到來時,再采樣PIN引腳的預(yù)加電平信號,將這兩路信號送到CXA2096N內(nèi)部的自動增益控制電路,經(jīng)差運(yùn)算后輸出。再對輸出信號進(jìn)行黑電平箝位、預(yù)消隱等處理,然后由CXA2096N的DRVOUT引腳輸出。DSP產(chǎn)生CXA2096N的工作時序。

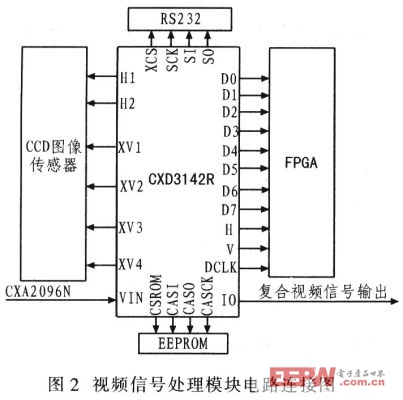

2.3.2 視頻信號處理(CXD3142R)

本設(shè)計采用SONY公司專用信號處理器件CXD3142R作為信號處理器。CXD3142R是專用于對Ye,Cv,Mg和G補(bǔ)色單片CCD輸出信號進(jìn)行處理的低功耗、高效率的信號處理器;具有自動曝光和自動白平衡功能,可同時輸出復(fù)合視頻信號和YUV 8位數(shù)字信號輸出。內(nèi)部集成9位A/D轉(zhuǎn)換器同步信號產(chǎn)生電路、外部同步電路和時鐘控制電路。此外,CXD3142R還具有串口通信功能,用戶可在PC機(jī)中預(yù)先設(shè)定好DSP中的寄存器值,通過串口下載到DSP,并對圖像信號進(jìn)行自動曝光和自動白平衡等處理。圖2為視頻信號處理模塊電路連接圖。

圖2中,H1,H2,XVl,XV2,XV3,XV4是CCD圖像傳感器的時序驅(qū)動信號,EEPROM用來存儲DSP初始化的寄存器值。D0~D7是YUV數(shù)字信號。其具體工作流程:將CCD圖像傳感器采集的模擬信號經(jīng)CXA2096N進(jìn)行相關(guān)預(yù)處理后,相應(yīng)數(shù)字信號經(jīng)VIN引腳傳給DSP(CXD3142),DSP接收數(shù)字信號后,利用其內(nèi)部AE/AWB檢測電路、同步信號產(chǎn)生電路、外同步電路以及相關(guān)算法對其進(jìn)行相關(guān)處理,處理完成后在行(H引腳)、場(V引腳)信號及時鐘信號(PCLK)的控制下將8位數(shù)字信號經(jīng)過D0~D7引腳傳給FPGA模塊進(jìn)行相關(guān)處理。通過引腳SCK、SI、SO、XCS串口通信,通過CSROM、CASI、CSASO、CASCK引腳與外部EEPROM通信,實現(xiàn)DSP相關(guān)的初始化。此外,IO引腳輸出經(jīng)DSP處理過的復(fù)合視頻信號,通過相關(guān)接口直接在CRT顯示器上顯示圖像處理結(jié)果。

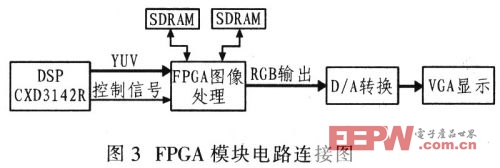

2.3.3 FPGA模塊

為了實現(xiàn)實時預(yù)處理數(shù)字視頻信號數(shù)據(jù),增加系統(tǒng)擴(kuò)展性,該系統(tǒng)設(shè)計擴(kuò)展一片由Xilinx公司生產(chǎn)的基于90 nm工藝制造的Spartan3E系列FPGA,其型號為XC3S250E-PQ208-4C,此FPGA具有較高的性價比,其內(nèi)有25萬個系統(tǒng)門,5508個邏輯單元(LC),612個可配置邏輯塊(CLB),216 Kbit的塊RAM,12個專用乘法器,158個可用的I/O接口,4個數(shù)字時鐘管理單元(DCM)。圖3為其電路連接圖。

DSP與FPGA的通信是由11根總線完成的,分別是8根數(shù)據(jù)線,行、場同步信號和數(shù)據(jù)時鐘總線。因為CXD3142RDSP輸出PAL(逐行倒相)制式的數(shù)字視頻信號,F(xiàn)PGA將此PAL制視頻信號轉(zhuǎn)換成VGA格式。首先將YUV(4:2:2)格式信號轉(zhuǎn)換成RGB(5:6:5)格式,然后利用2個SDRAM作為幀緩存,利用場間插值算法,完成隔行到逐行的轉(zhuǎn)換,并將幀率由25 Hz提升到60 Hz,同時產(chǎn)生SVGA格式、幀頻為60 Hz的行、場同步信號,并把被放大的圖像數(shù)據(jù)經(jīng)D/A轉(zhuǎn)換后輸出到VGA接口,VGA顯示器上實時顯示采集的圖像。

2.4 外圍接口模塊

本設(shè)計支持RS-232C串口通信。但該串口通信需把3.3 V邏輯電平轉(zhuǎn)化成RS-232C標(biāo)準(zhǔn)電平。因此采用SP3232E系列器件完成電平轉(zhuǎn)換。SP3232E可從+3.0~+5.5 V的電源電壓產(chǎn)生2Vce的RS-232C電壓電平。該系列適用于+3.3 V系統(tǒng)。SP3232E器件的驅(qū)動器滿載時典型數(shù)據(jù)速率為235 kb/s。圖4為系統(tǒng)設(shè)計的接口電路圖。

需要注意的是,由于采用SP3232E器件,其驅(qū)動能力有限,該接口電路只適用于近距離傳輸。如果要進(jìn)行遠(yuǎn)距離傳輸,則必須加強(qiáng)信號傳輸能力。

3 系統(tǒng)硬件調(diào)試

系統(tǒng)硬件調(diào)試應(yīng)先調(diào)試電源模塊,如果系統(tǒng)電源錯誤,器件將損壞;然后調(diào)試DSP模塊。DSP上電后,空閑情況下一般不會發(fā)熱,若有輕微的發(fā)熱情況應(yīng)立即斷開電源以免損壞DSP器件,其主要原因是把DSP的工作電壓接到DSP的非電壓引腳。DSP的工作電壓正常后,再檢查復(fù)位電路、時鐘電路是否正確。如果DSP的時鐘引腳無信號,一般是電路虛焊。如果有信號,但工作頻率達(dá)不到系統(tǒng)工作的正常值,則通過調(diào)整外部可調(diào)電容。如果還達(dá)不到要求,則應(yīng)考慮時鐘信號是否受到低頻信號干擾,就要認(rèn)真檢查電路板,必要時應(yīng)修改布線。FPGA模塊的調(diào)試與上述方法相同。

4 結(jié)論

該系統(tǒng)設(shè)計已成功應(yīng)用于數(shù)字視頻展臺項目。目前該產(chǎn)品已投入生產(chǎn),但圖像質(zhì)量還有待提高,可能是模擬視頻信號失真和白平衡的值設(shè)置不恰當(dāng)。該設(shè)計方案具有較強(qiáng)的靈活性,還可應(yīng)用于監(jiān)控、安防等產(chǎn)品開發(fā)。

評論