本文引用地址:http://www.ex-cimer.com/article/180291.htm

3 結語

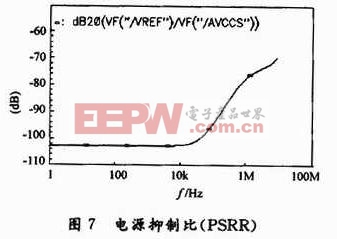

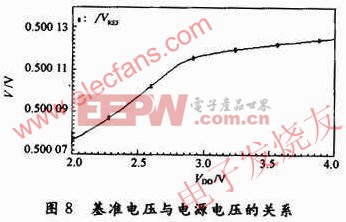

帶隙基準電壓電路作為模擬電路中的重要模塊對A/D采集精度��、電源管理芯片的性能都有重要影響。本文設計了一種高精度��、高電源抑制比����、低電壓的帶隙基準電路��,并且實現(xiàn)了對基準電壓的外部修調(diào)��。結果表明:電路在3.3 V電源電壓����,-40~+125℃下能提供穩(wěn)定的0.5 V基準電壓輸出,溫漂15 ppm��,低頻時電源抑制比-103 dB����,達到了設計要求。

DIY機械鍵盤相關社區(qū):機械鍵盤DIY

評論