FPGA/CPLD狀態(tài)機(jī)的穩(wěn)定性設(shè)計(jì)

隨著大規(guī)模和超大規(guī)模FPGA/CPLD器件的誕生和發(fā)展,以HDL(硬件描述語言)為工具、FPGA/CPLD器件為載體的EDA技術(shù)的應(yīng)用越來越廣泛.從小型電子系統(tǒng)到大規(guī)模SOC(Systemonachip)設(shè)計(jì),已經(jīng)無處不在.在FPGA/CPLD設(shè)計(jì)中,狀態(tài)機(jī)是最典型、應(yīng)用最廣泛的時(shí)序電路模塊,如何設(shè)計(jì)一個(gè)穩(wěn)定可靠的狀態(tài)機(jī)是我們必須面對的問題.

本文引用地址:http://www.ex-cimer.com/article/151512.htm1、狀態(tài)機(jī)的特點(diǎn)和常見問題

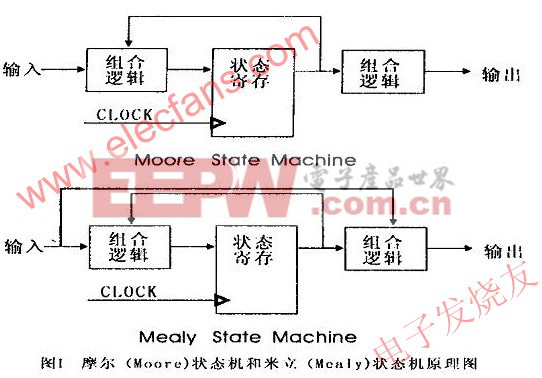

標(biāo)準(zhǔn)狀態(tài)機(jī)分為摩爾(Moore)狀態(tài)機(jī)和米立(Mealy)狀態(tài)機(jī)兩類.Moore狀態(tài)機(jī)的輸出僅與當(dāng)前狀態(tài)值有關(guān),且只在時(shí)鐘邊沿到來時(shí)才會(huì)有狀態(tài)變化.Mealy狀態(tài)機(jī)的輸出不僅與當(dāng)前狀態(tài)值有關(guān),而且與當(dāng)前輸入值有關(guān),這一特點(diǎn)使其控制和輸出更加靈活,但同時(shí)也增加了設(shè)計(jì)復(fù)雜程度.其原理如圖1所示.

根據(jù)圖1所示,很容易理解狀態(tài)機(jī)的結(jié)構(gòu).但是為什么要使用狀態(tài)機(jī)而不使用一般時(shí)序電路呢?這是因?yàn)樗哂幸恍┮话銜r(shí)序電路無法比擬的優(yōu)點(diǎn).

用VHDL描述的狀態(tài)機(jī)結(jié)構(gòu)分明,易讀,易懂,易排錯(cuò);

相對其它時(shí)序電路而言,狀態(tài)機(jī)更加穩(wěn)定,運(yùn)行模式類似于CPU,易于實(shí)現(xiàn)順序控制等.

用VHDL語言描述狀態(tài)機(jī)屬于一種高層次建模,結(jié)果經(jīng)常出現(xiàn)一些出乎設(shè)計(jì)者意外的情況:

在兩個(gè)狀態(tài)轉(zhuǎn)換時(shí),出現(xiàn)過渡狀態(tài).

在運(yùn)行過程中,進(jìn)入非法狀態(tài).

在一種器件上綜合出理想結(jié)果,移植到另一器件上時(shí),不能得到與之相符的結(jié)果.

狀態(tài)機(jī)能夠穩(wěn)定工作,但占用邏輯資源過多.

在針對FPGA器件綜合時(shí),這種情況出現(xiàn)的可能性更大.我們必須慎重設(shè)計(jì)狀態(tài)機(jī),分析狀態(tài)機(jī)內(nèi)在結(jié)構(gòu),在Moore狀態(tài)機(jī)中輸出信號是當(dāng)前狀態(tài)值的譯碼,當(dāng)狀態(tài)寄存器的狀態(tài)值穩(wěn)定時(shí),輸出也隨之穩(wěn)定了.經(jīng)綜合器綜合后一般生成以觸發(fā)器為核心的狀態(tài)寄存電路,其穩(wěn)定性由此決定.如果CLOCK信號的上升沿到達(dá)各觸發(fā)器的時(shí)間嚴(yán)格一致的話,狀態(tài)值也會(huì)嚴(yán)格按照設(shè)計(jì)要求在規(guī)定的狀態(tài)值之間轉(zhuǎn)換.然而這只是一種理想情況,實(shí)際CPLD/FPGA器件一般無法滿足這種苛刻的時(shí)序要求,特別是在布線后這些觸發(fā)器相距較遠(yuǎn)時(shí),CLOCK到達(dá)各觸發(fā)器的延時(shí)往往有一些差異.這種差異將直接導(dǎo)致狀態(tài)機(jī)在狀態(tài)轉(zhuǎn)換時(shí)產(chǎn)生過渡狀態(tài),當(dāng)這種延時(shí)進(jìn)一步加大時(shí),將有可能導(dǎo)致狀態(tài)機(jī)進(jìn)入非法狀態(tài).這就是Moore狀態(tài)機(jī)的失效機(jī)理.對于Mealy狀態(tài)機(jī)而言,由于其任何時(shí)刻的輸出與輸入有關(guān),這種情況就更常見了.

2 狀態(tài)機(jī)設(shè)計(jì)方案比較

2.1 采用枚舉數(shù)據(jù)類型定義狀態(tài)值

在設(shè)計(jì)中定義狀態(tài)機(jī)的狀態(tài)值為枚舉數(shù)據(jù)類型,綜合器一般把它表示為二進(jìn)制數(shù)的序列,綜合后生成以觸發(fā)器為核心的狀態(tài)寄存電路,寄存器用量會(huì)減少,其綜合效率和電路速度將會(huì)在一定程度上得到提高.

例1 定義狀態(tài)值為枚舉類型的狀態(tài)機(jī)VHDL程序.

library ieee;

use ieee.std_logic_1164 all;

entity example is

port(clk:in std_logic;

mach_input:in std_logic;

mach_outputs:out std_logic_vector(0 to 1));

end example;

architecture behave of example is

type states is(st0,st1,st2,st3); --定義states為枚舉類型

signal current_state,next_state:states;

begin

state_change:process(clk) --狀態(tài)改變進(jìn)程

begin

評論