FPGA/CPLD狀態(tài)機的穩(wěn)定性設計

wait until clk'event and clk='1';

current_state=next_state;

end process state_change;

combination:process(current_state,mach_input)

…… --輸出狀態(tài)值譯碼,給next_state賦新值.省略

end behave;

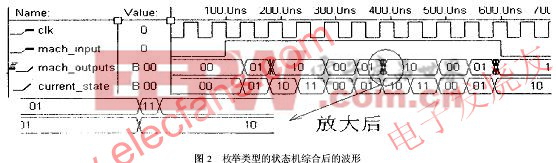

圖2 枚舉類型的狀態(tài)機綜合后的波形

例1是一個四狀態(tài)全編碼狀態(tài)機,綜合后的仿真波形如圖2所示.從放大后的局部可以看出輸出狀態(tài)值從“01”到“10”轉換過程中出現(xiàn)了過渡狀態(tài)“11”.從微觀上分析中間信號“Current_state”狀態(tài)轉換過程,狀態(tài)寄存器的高位翻轉和低位翻轉時間是不一致的,當高位翻轉速度快時,會產(chǎn)生過渡狀態(tài)“11”,當?shù)臀环D速度快時會產(chǎn)生過渡狀態(tài)“00”.若狀態(tài)機的狀態(tài)值更多的話,則產(chǎn)生過渡狀態(tài)的概率更大.如果在非全編碼狀態(tài)機中,由于這種過渡狀態(tài)的反饋作用,將直接導致電路進入非法狀態(tài),若此時電路不具備自啟動功能,那么電路將無法返回正常工作狀態(tài).

因為狀態(tài)機的輸出信號常用作重要的控制,如:三態(tài)使能,寄存器清零等.所以這種結果是不允許的,如何消除此類過渡狀態(tài)呢?方法之一是采用格雷碼表示狀態(tài)值.

2.2 用格雷碼表示狀態(tài)值

格雷碼的特點是任意相鄰兩個數(shù)據(jù)之間只有一位不同,這一特點使得采用格雷碼表示狀態(tài)值的狀態(tài)機,可以在很大程度上消除由延時引起的過渡狀態(tài).將例1改進之后的程序如例2.

例2 采用格雷碼表示狀態(tài)值的狀態(tài)機.

library ieee;

use ieee.std_logic_1164 all;

entity example is

port(clk:in std_logic;

mach_input:in std_logic;

mach_outputs:out std_logic_vector(0 to 1));

end example;

architecture behave of example is

constant st0:std_logic_vector(0 to 1):=00;

constant st1 :std_logic_vector(0 to 1):=01;

constant st2:std_logic_vector(0 to 1):=11;

constant st3:std_logic_vector(0 to 1):=10;

signal current_state,next_state:std_logic

vector(0to1);

begin

……

endbebave;

采用該方法,寄存器的狀態(tài)在相鄰狀態(tài)之間跳轉時,只有一位變化,產(chǎn)生過渡狀態(tài)的概率大大降低.但是當一個狀態(tài)到下一個狀態(tài)有多種轉換路徑時,就不能保證狀態(tài)跳轉時只有一位變化,這樣將無法發(fā)揮格雷碼的特點.

2.3 定義“ONEHOT”風格的狀態(tài)值編碼

雖然VHDL語言的目標之一是遠離硬件,但是到目前為止并沒有完全實現(xiàn),所以VHDL程序在針對不同的器件綜合時,仍然會有很大差異.特別是FPGA器件,當我們采用格雷表示狀態(tài)值,描述一個簡單的狀態(tài)機時,就可能出現(xiàn)不穩(wěn)定結果.在針對FPGA器件寫程序時,我們可以將狀態(tài)值定義為“ONEHOT”風格的狀態(tài)碼,將上例稍作修改,見例3.

例3 采用“ONEHOT”編碼的狀態(tài)機

library ieee;

use ieee std_logic_1164.all;

entity example is

port(clk:in std_logic;

評論