2 特性模擬

2.1 閾值電壓特性

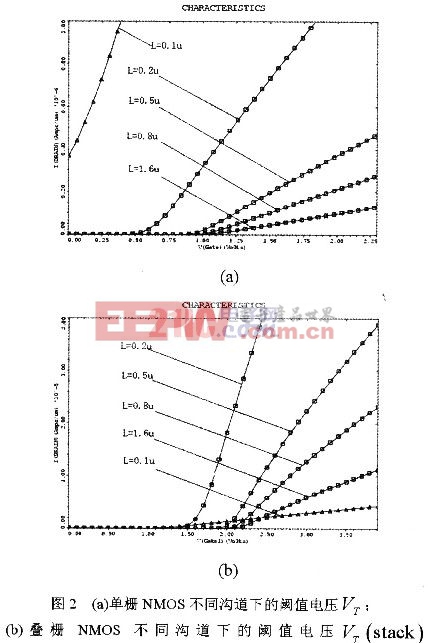

首先,我們用模擬軟件MEDICI仿真了疊柵MOSFET與單柵MOSFET的閾值電壓�,對仿真結果做比較,將不同溝道長度閾值電壓特性以及閾值電壓的變化率展現(xiàn)出來�。所用的兩種結構除了柵結構不同外,其它參數(shù)都相同(如溝道摻雜情況�、源漏情況、溝長等)�。具體摻雜數(shù)值如表1,

為了仿真其閾值電壓特性,接法上將源端�、襯底接地,漏端加一個較小電壓VDS=0.10V�,單柵氧化層厚度tox=2.0×10-6cm,疊柵的兩個柵氧化層厚度都是tox=2.0×10-6cm�。仿真結果如圖2所示。

電容傳感器相關文章:電容傳感器原理

評論