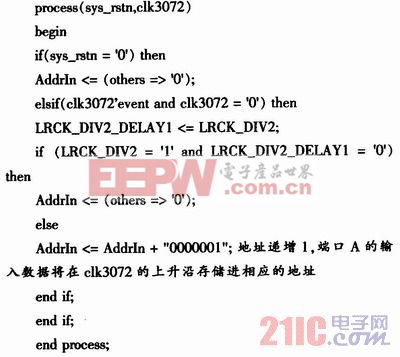

在端口A輸入時鐘clk3072的每個下降沿����,端口A輸入地址AddrIn都遞增1,則在elk3072的上升沿�,根據(jù)例化的雙口RAM的IP核,端口A的四路輸入數(shù)據(jù)將存儲進相應的地址空間中��。

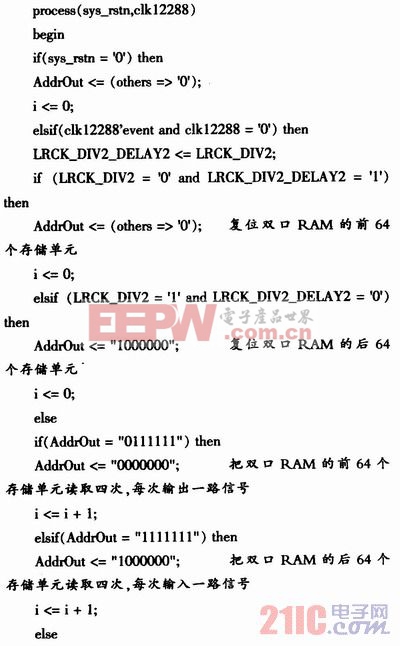

在端口B輸入時鐘elk12288的每個下降沿����,端口B輸入地址AddrOut都遞增1�,則在elk12288的上升沿,根據(jù)例化的雙口RAM的IP核,相應的地址空間中的數(shù)據(jù)將通過Dout被讀出來��。

依次將輸出數(shù)據(jù)以時分多址的幀格式傳輸出去�。

評論