利用縫隙抑制型鎢填充接觸區(qū)工藝來(lái)降低良率損失

作者:應(yīng)用材料公司金屬沉積產(chǎn)品事業(yè)部接觸和中段產(chǎn)品線全球經(jīng)理Jonathan Bakke

在早先的技術(shù)節(jié)點(diǎn)中,由于器件尺寸較大,能采用成核及平整化化學(xué)氣相沉積(CVD)技術(shù)進(jìn)行鎢(W)填充。如今,由于插塞處的超小開(kāi)口很容易發(fā)生懸垂現(xiàn)象,因此薄膜表面均勻生長(zhǎng)的共形階段可能在填充完成前就關(guān)閉或夾斷,從而留下孔洞。即使沒(méi)有孔洞,由于填充物從側(cè)壁生長(zhǎng),在共形沉積時(shí)必然會(huì)在中間形成中心縫隙問(wèn)題。

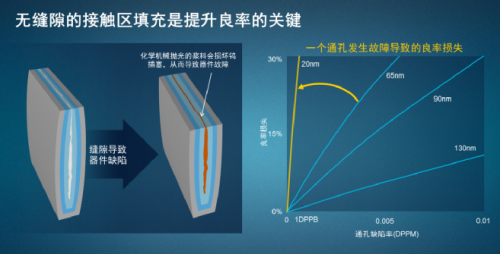

這些屬性使極細(xì)小的成核層在化學(xué)機(jī)械拋光(CMP)過(guò)程中容易被滲透,使CMP漿料進(jìn)入,從而破壞鎢插塞。這會(huì)導(dǎo)致高電阻產(chǎn)生,或使得負(fù)責(zé)傳遞晶體管信號(hào)的互連完全損壞。先進(jìn)芯片設(shè)計(jì)中的高密度特征以及缺乏多余的通孔,意味著一個(gè)簡(jiǎn)單的孔洞就會(huì)造成器件完全損壞,從而帶來(lái)嚴(yán)重的良率損失(圖1)。

圖1:上圖中,y軸顯示了器件的良率損失,x軸為通孔缺陷率。十億分之一的缺陷就會(huì)導(dǎo)致20nm節(jié)點(diǎn)的芯片產(chǎn)生15%以上的良率損失,而在更小節(jié)點(diǎn)的器件中這一情況會(huì)更為嚴(yán)重。

我們的新方法采用了獨(dú)特的“選擇性”抑制機(jī)制,可生成自下而上的填充,而不會(huì)產(chǎn)生縫隙和孔洞問(wèn)題。對(duì)成核層的上部區(qū)域進(jìn)行特殊的預(yù)處理可促成鎢自下而上生長(zhǎng),從而盡可能減少因夾斷而造成的孔洞或接觸區(qū)縫隙的產(chǎn)生。

這一“縫隙抑制型鎢填充工藝”(SSW)有效優(yōu)化了鎢的體積,可制成更牢固的成核表面,便于填充后續(xù)的集成工序。這樣也可以降低對(duì)CMP和介質(zhì)蝕刻工藝的要求,從而帶來(lái)性能、產(chǎn)品設(shè)計(jì)和良率方面的改善。

評(píng)論