基于FPGA的多路脈沖重復(fù)頻率跟蹤器

2.2 FPGA芯片的配置

APEX系列FPGA芯片是基于SRAM技術(shù)的器件,由于SRAM的易失性,掉電以后芯片中的配置信息將丟失,所以每次系統(tǒng)上電時(shí)都要重新加載配置數(shù)據(jù)Altera公司提供了一系列的配置器件用于儲存配置數(shù)據(jù)并且在上電時(shí)加載FPGA本設(shè)計(jì)選用Altera公司的EPC2,最大的優(yōu)勢在于EPC2是FLASH器件,可以多次重復(fù)編程,改掉了以前的PROM配置器件只能寫入一次的缺點(diǎn),極大地方便了系統(tǒng)調(diào)試和產(chǎn)品升級當(dāng)設(shè)計(jì)完成的產(chǎn)品需要改進(jìn)時(shí),只需將EPC2中的內(nèi)容重寫一遍即可,縮短了產(chǎn)品的研發(fā)周期

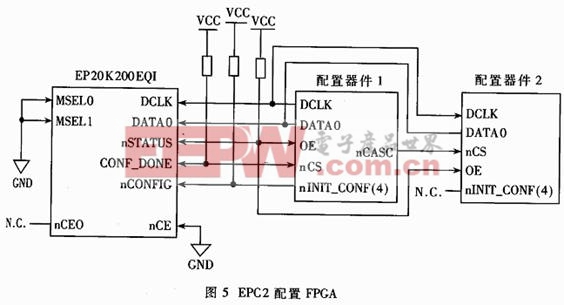

在設(shè)計(jì)中需要注意的是EPC2的容量是1.6Mb,根據(jù)FPGA芯片的容量大小需要的配置芯片的數(shù)目是不等的本設(shè)計(jì)中采用的EP20K200EQI芯片的容量是1.9Mb,所以需要兩片EPC2圖5是用兩片EPC2配置EP20K200EQI芯片的連線圖,通過EPC2芯片的nCASC管腳,可以方便地實(shí)現(xiàn)多片級聯(lián)系統(tǒng)上電后, EP20K200EQI芯片檢測到nCONFIG管腳電平由低到高的跳變時(shí),啟動配置流程首先EP20K200EQI芯片驅(qū)動CONF_DONE管腳為低,將第一片EPC2的nCS管腳拉低,選通該芯片經(jīng)過一段延時(shí)以后EP20K200EQI芯片釋放nSTATUS管腳,上拉電阻將EPC2的OE管腳拉成高電平將其使能EPC2用其內(nèi)部振蕩器將配置數(shù)據(jù)串行輸出到FPGA芯片中當(dāng)?shù)谝黄珽PC2的全部數(shù)據(jù)輸出完后,它驅(qū)動nCASC管腳為低,按順序驅(qū)動第二個(gè)EPC2的nCS為低,啟動第二個(gè)EPC2輸出數(shù)據(jù)前一個(gè)EPC2啟動下一個(gè)EPC2的過程在一個(gè)時(shí)鐘周期內(nèi)就可以完成,所以輸送給FPGA芯片的數(shù)據(jù)流是連續(xù)的

2.3 FPGA芯片的在線編程

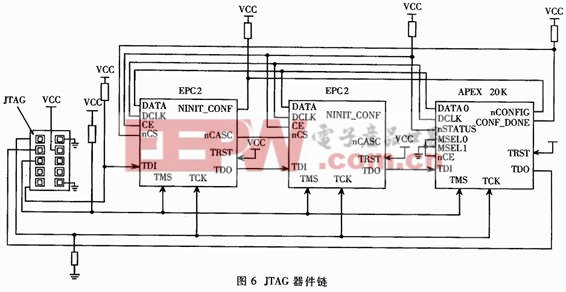

APEX系列FPGA芯片在邊界掃描模式(JTAG模式)下可以對其進(jìn)行在線的配置重構(gòu),系統(tǒng)無需重新上電就可以修改FPGA芯片的配置,極大地方便了調(diào)試JTAG模式也可以對EPC2進(jìn)行在線編程在系統(tǒng)設(shè)計(jì)時(shí),可以把多個(gè)器件組成一個(gè)JTAG器件鏈,用一個(gè)JTAG兼容頭(例如Altera的ByteBlasterMV并口下載電纜)把所有的器件連接起來JTAG器件鏈方式特別適合電路板上有多個(gè)器件的情況,用一個(gè)JTAG頭就可以對多個(gè)器件進(jìn)行在線編程本設(shè)計(jì)中電路板上有三個(gè)JTAG器件,包括兩片EPC2和一片F(xiàn)PGA,設(shè)計(jì)的JTAG器件鏈如圖6所示

濾波器相關(guān)文章:濾波器原理

fpga相關(guān)文章:fpga是什么

濾波器相關(guān)文章:濾波器原理

合成孔徑雷達(dá)相關(guān)文章:合成孔徑雷達(dá)原理 脈沖點(diǎn)火器相關(guān)文章:脈沖點(diǎn)火器原理

評論